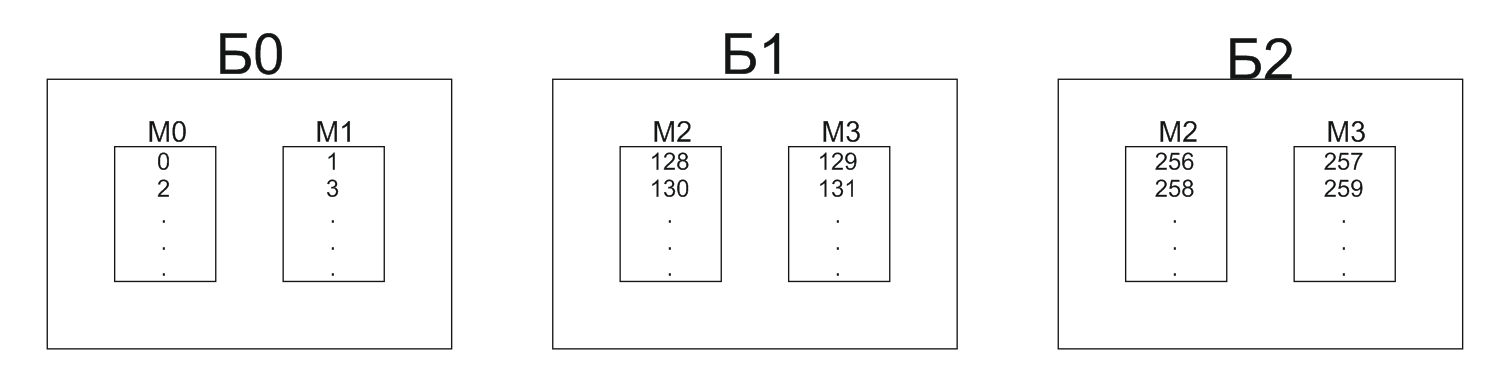

Структура основной памяти на основе блочной схемы

Рисунок 16 Структура

основной памяти на основе блочной схемы

Адресное пространство

памяти разбито на группы последовательных

адресов, и каждая такая группа

обеспечивается отдельным банком памяти.

Для обращения к основной памяти

используется 9-разрядный адрес, 7 младших

разрядов которого A6-A0

поступают параллельно на ячейку 2

старшего разряда. Разряды А8-А7 содержат

№ банка. Выбор банка обеспечивается

либо с помощью динамического номера

банка, либо путем мультиплексирования

информации.

Ёмкость

такого ЗУ равна сумме ёмкостей

составляющих, а быстродействие равно

быстродействию его отдельного банка.

Циклическая организация

Большей

скоростью доступа к основной памяти

можно достичь за счет одновременного

доступа к многим банкам памяти. Одна из

использующихся для этого методик

называется расслоением памяти. В её

основе лежит чередование адресов,

обеспечивающееся за счет циклического

разбиения адреса.

Рисунок 17 Циклическая

схема расслоения памяти

В

данном случае для выбора банка используется

А1-А0, для выбора ячейки А8-А2. Поскольку

в каждом таком такте на ША может

присутствовать только адрес одной

ячейки, параллельное обращение к

нескольким банкам невозможно, однако

оно может быть организовано со сдвигом

на 1 такт. Адрес ячейки запоминается в

индивидуальном регистре адреса, а

дальнейшие операции по доступу к ячейке

в каждом банке протекают независимо.

Блочно-циклическая схема расслоения памяти

Каждый

банк состоит из нескольких модулей,

адресуемых по круговой схеме. Адреса

между банком распространены по блочной

схеме. Адресные ячейки разбиваются на

3 части: старшие биты определяющие номер

банка, следующая группа разрядов

указывает на ячейку модуля, а младшие

биты выбирают модуль в банке.

Рисунок 18

Блочно-циклическая схема расслоения

памяти

Архитектура с сокращенным набором команд

Основные

черты RISC-архитектуры:

-

Выполнение всех

команд за 1 цикл; -

Стандартная

однословная длина команд, равная

естественной длине слова и ширине ШД,

допускающая унифицированную поточную

обработку; -

Малое число команд;

-

Малое количество

форматов команд; -

Доступ к памяти

только посредством команд чтения и

записи; -

Все команды, за

исключением чтения и записи, используют

внутри процессорные межрегистровые

пересылки; -

Устройство

управления с жесткой логикой; -

Большой процессорный

файл регистров общего назначения;

КлассSimd

Векторные и векторно-конвейерные

вычислительные системы

Понятие вектора и размещение данных в

памяти

В средствах

векторной обработки под вектором

понимается 1-мерный массив однотипных

данных, регулярным образом размещенным

в памяти ВС.

Если обработке

подвергаются многомерные массивы, их

так же рассматривают как векторы. При

размещении матрицы в памяти все её

элементы заносятся в ячейки с

последовательными адресами, причем

возможно размещение как по строкам, так

и по столбцам.

Понятие векторного процесса

Векторные

процессор – процессор, в котором

операндами некоторой команды могут

выступать упорядоченные массивы данных,

т.е. векторы.

Векторные

процессоры могут быть реализованы в

двух вариантах:

-

Как дополнительных

блок к универсальной ВС; -

Как основа

самостоятельной ВС;

Обобщенная структура векторного

процессора

Рисунок 19 Обобщенная

структура векторного процессора

Обработка всех n

компонентов векторов-операндов задается

одной векторной командой. Элементы

векторов представляются числами в форме

с плавающей запятой. АЛУ векторного

процессора может быть реализовано в

виде единого конвейерного устройства,

способного выполнять все предусмотренные

операции над числами с плавающей запятой,

однако чаще всего АЛУ состоит из отдельных

блоков сложения и умножения, каждый из

которых конвейеризирован. Кроме того,

в состав векторной ВС включается и

скалярный процессор, что позволяет

выполнять векторные и скалярные команды.

Для хранения операций используется

векторные регистры, представляющие

собой совокупность скалярных регистров,

объединенных в очередь FIFO.

Система

команд векторного процессора поддерживает

работы с векторными регистрами и включает

следующие команды:

-

Загрузка векторного

регистра содержимым последовательных

ячеек памяти; -

Выполнение операций

над всеми элементами векторов; -

Сохранение

содержимого векторного регистра в

последовательности ячеек памяти;

Регистр длины

вектора (РДВ) – определяет, сколько

элементов содержит обрабатываемый в

данный момент вектор, т.е. сколько

индивидуальных операций с элементами

нужно сделать.

Регистр максимальной

длины вектора (РМД) – определяет

максимальное число элементов вектора,

которое может быть одновременно

обработано аппаратурой процессора.

Регистр маски

вектора – каждому элементу вектора

соответствует 1 бит. Установка бита в 1

разрешает запись соответствующего

элемента вектора результата в выходной

регистр.

Для обработки

только ненулевых элементов вектора в

системе команд вектора процессора

предусмотрены опции упаковки и распаковки.

Операция упаковки формирует вектор,

содержащий только ненулевые элементы

исходного вектора, операция распаковки

– обратное представление. Данные задачи

процессора выполняются с помощью

регистра векторов индекса (РВИ), нулевое

значение бита которого свидетельствует,

что соответствующий элемент исходного

вектора равен нулю.

Соседние файлы в папке LektsiiProshkina

- #

- #

- #

- #

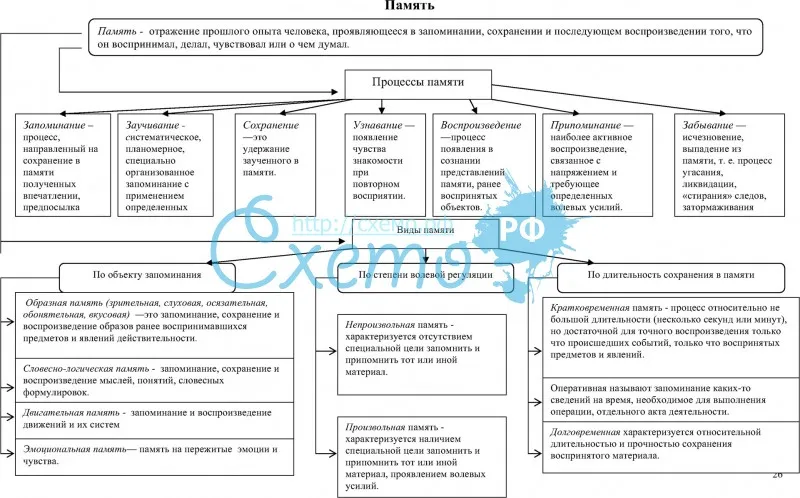

- Структурно-логические схемы

- Психология

- Память

Память

Скачать схему без водяного знака

669

admin

Смотрите также

Двигательная, образная, эмоциональная, смысловая память

Произвольная и непроизвольная память

Кратковременная, оперативная, долговременная память

Высшая нервная деятельность (инстинкты, память, сон)

Блок памяти

|

Вместе с этим смотрят:

Ввод текста

Вероятностный подход к измерению информации

Видеоадаптеры EGA, VGA

Виртуальный мир

Схемы

Если вы хотите разобраться в принципе работы машины, то лучшим способом это сделать, будет разобрать её, заглянуть внутрь, своими глазами увидеть все движущиеся детали и понять, как она работает. Вторым способом будет изучение документации с обилием картинок и пояснений о взаимодействии всех узлов и агрегатов.

Компьютер тоже машина, но единственное, что в нём движется – это невидимое и тихое электричество. В общем, смотреть внутрь компьютера совсем не интересно, так как визуально, в нём ничего не происходит.

На самом деле, устройство и изготовление отдельных частей компьютера – это очень интересный предмет. Но здесь мы ограничимся лишь тем, что в начале процесса имеется кремниевая пластина, затем после различных химических реакций, металлизации и резки, получается полупроводниковая пластина с маленькими квадратными кристаллами – «Чипами».

На этих чипах нанесены все необходимые логические элементы. Каждый такой чип помещают в пластиковый корпус и подключают к нему металлические ножки – «Выводы». На выходе готовой продукции получается микросхема.

Вот так под микроскопом выглядит знаменитый процессор MOS6502.

Структура настоящего чипа довольно сложная и крайне загромождена. Разобраться с принципом действия устройства, таким образом, будет крайне затруднительно. Да и опять-таки, электричество или признаки его деятельности мы всё равно не увидим.

Поэтому остаётся лишь один способ – изучение схемы.

Запомни это!

Скорее всего, вы слышали о компьютерной памяти. Итеперьмы узнаем, что она из себя представляет. Поскольку единственное, что есть внутри компьютера, это биты, их состояние (включены или выключены) и изменение их состояния, то память может «запоминать» только эти простые вещи. Сейчас мы узнаем, как это происходит.

Следующая схема отображает один бит компьютерной информации. Сохранить бит можно с помощью очередного трюка с логическим элементом И-НЕ. Мы посмотрим, как это работает в данном примере, затем в целом блоке таких элементов, где можно сохранить уже большее количество полезной информации.

В целом, эта комбинация имеет два входа и один выход. Вход ‘i’ отвечает за ввод бита, который нужно запомнить. Вход ‘s’ служит для сообщения, когда нужно запоминать бит. Выход ‘o’ служит для вывода бита из памяти.

Итак, что мы получили? Если ‘s’ включен, ‘o’ повторяет всё, что приходит на ‘i’, а если ‘s’ выключен, ‘o’ остаётся в последнем состоянии, независимо от того, что происходит на ‘i’. Вот так и устроена вся память компьютера. Она призвана помнить состояние битов в определённый момент. Думаю, теперь вам ясно, как работает память компьютера. Поэтому мы больше не станем прибегать к такой громоздкой схеме, а станем использовать схему попроще:

Здесь ‘s’, ‘i’ и ‘o’ так же означают: «разрешение записи», «вход записываемого бита» и «выход записанного бита», соответственно. ‘M’ – значит «Память» (Memory – англ. «Память»). Всё опять просто. Не правда ли?

Что делать с битом?

Теперь мы знаем, как сохранить бит и как его потом «вспомнить». И что теперь с этим делать? С помощью бита можно что-либо включить или выключить. Например, в памяти кофе-машины есть три бита, отвечающие за приготовление определённого вида кофе и в зависимости от того, какой бит мы включим, она приготовит нам один определённый вид кофе из трёх. Сам по себе бит ничего не значит. Чтобы от его состояния что-то зависело, нужно чтобы при определённом его значении запускалось что-то извне, какой-то следующий в схеме механизм или алгоритм. Бит может быть предназначен для чего угодно. А вот для чего именно, должен решить кто-то другой. Так с помощью одного бита можно регулировать пешеходный светофор: бит включен – светофор зеленый, выключен – красный. Казалось бы, бит влияет на движение пешеходов по зебре, но на самом деле всё не совсем так. Люди реагируют на сигнал светофора, а тот в свою очередь, срабатывает благодаря специальному устройству, которое считывает тот самый бит, в котором просто хранится одно из двух состояний. Вот так один маленький бит может запустить целую цепь событий и взаимодействий механизмов. При всём этом сам бит ничего не делает, только хранит определенное состояние.

Как розу ты не назови…

Прежде всего, начнём с небольших изменений в некоторых названиях. Мы уже знаем, что в компьютере везде используется принцип присутствия либо отсутствия электричества. И мы называли эти состояния «включено» и «выключено». Несмотря на то, что эти слова короткие и простые, для этих двух состояний придумали названия ещё проще и короче. Теперь мы будем «выключено» называть 0, а «включено» будем называть 1. Конечно, в некоторых моментах удобнее будет говорить именно «включено» или «выключено», но в основном куда удобнее использовать 1 и 0. Например, таблица истинности нашего старого знакомого И-НЕ выглядит так:

Здесь нужно уточнить, что с этого момента ничего не изменилось и внутри компьютера никаких цифр не появилось. Мы просто говорим 1, подразумевая «ВКЛ» и говорим 0, подразумевая «ВЫКЛ». Это просто общепринятое обозначение. Именно это, кстати говоря, и изображается на кнопках включения электрических приборов:

Вот видите, если на кнопке чайника написано 1 и 0, то это совсем не значит, что внутри него есть какие-то цифры.

Восемь – достаточно

Чтобы сохранить нечто большее, чем просто «Да» или «Нет», давайте создадим блок из восьми простейших битов памяти. У каждого бита есть свой собственный вход данных и собственный выход, а все разрешающие контакты соединены одним проводом. Слева подробная схема соединения однобитной памяти. Справа все тоже самое, только имеет упрощенный вид (проще чертить и проще читать).

Уданной сборки есть своё собственное название «Байт» (англ. Byte – укус). Поэтому на сборке справа буква ‘B’. Естьнесколько противоречивых историй возникновения этого названия. Но мы можем точно сказать, что у первых компьютерных дизайнеров явно было чувство юмора, так как единица информации названа бит/bit – чуток, полубайт/nibble (4 бита) – щипок, байт/byte(8 бит) –укус.

Если раньше у нас был всего один бит, а его состояние «выключено» мы теперь называем 0, то теперь у нас есть целый байт, одно из состояний которого можно записать так: 0000 0000. Теперь понимаете, почему мы перешли на 0 и 1?

Зачем же нужен байт? Когда мы используем всего один бит, мы можем получить всего два варианта сохраняемой информации: 0 или 1. А теперь представим, что у нас сборка из двух бит. Теперь у нас куда больше вариантов:

Был один бит с двумя состояниями, стало два бита с четырьмя. Т.е. 00, 01, 10 и 11. На самом деле, количество вариантов (информации) можно посчитать по простой формуле: 2^количечтво бит в сборке. Т.е. в сборке из двух бит 2^2=4. Сходится? Заранее можно посчитать, что три бита дадут нам 2^3=8 вариантов, четыре бита в сборке дадут 2^4=16, а восемь бит 2^8=256 возможных состояний, девять бит 2^9=512 и так далее.

Часть 1 – Назад Далее – Часть 3

Министерство Путей Сообщения

РОССИЙСКИЙ ГОСУДАРСТВЕННЫЙ ОТКРЫТЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ ПУТЕЙ СООБЩЕНИЯ

Воронежский Филиал

КУРСОВАЯ РАБОТА

ПО СХЕМОТЕХНИКЕ

на тему: “Разработка блока памяти микропроцессорной системы”

|

Выполнил: студент 3 курса Бобкин И. Г. уч. шифр: 96 – ВЭВМ – 810 |

|

Рецензент: к.т.н. доцент Ермаков А .Е. |

ВОРОНЕЖ

1999

СОДЕРЖАНИЕ

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА……………………………………………………………………. 3

1. Задание на курсовое проектирование………………………………………………………. 3

2. Особенности построения блоков памяти………………………………………………….. 4

3. Описание принципов работы разрабатываемых блоков……………………………. 6

3.1. Разработка электрических схем блоков ПЗУ и ОЗУ……………………………. 6

3.2. Разработка селектора адреса…………………………………………………………….. 8

3.3. Временная диаграмма работы БП…………………………………………………….. 9

4. Расчет электрических параметров блока памяти…………………………………….. 10

ГРАФИЧЕСКАЯ ЧАСТЬ…………………………………………………………………………….. 12

1. Функциональная схема блока памяти…………………………………………………….. 12

Литература……………………………………………………………………………………………… 14

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА.

1. Задание на курсовое проектирование

Разработать блок памяти микропроцессорной системы,

где: объём ПЗУ составляет 20К*8 и строится на микросхемах К556РТ20

объём ОЗУ составляет 10К*8 и строится на микросхемах К132РУ9А

серия микросхем используемых в качестве дешифраторов,

буферов шин и т.д. – 1554

Режимы работы блока памяти определяются внешними управляющими сигналами MEMWR, MEMRD.

2. Особенности построения блоков памяти

Компактная микроэлектронная “память” широко применяется в современной электронной аппаратуре самого различного назначения. В ЭВМ память определяют как функциональную часть, предназначенную для записи, хранения и выдачи команд и обрабатываемых данных. Комплекс технических средств, реализующих функцию памяти, называют запоминающим устройством (ЗУ).

Для обеспечения работы процессора (микропроцессора) необходимы программа, т. е. последовательность команд, и данные, над которыми процессор производит предписываемые командами операции. Команды и данные поступают в основную память ЭВМ через устройство ввода, на выходе которого они получают цифровую форму представления, т. е. форму кодовых комбинаций О и 1. Основная память, как правило, состоит из ЗУ двух видов — оперативного (ОЗУ) и постоянного (ПЗУ).

Оперативное ЗУ предназначено для хранения переменной информации, оно допускает изменение своего содержимого в ходе выполнения процессором вычислительных операций с данными. Это значит, что процессор может выбрать (режим считывания) из ОЗУ код команды и данные и после обработки поместить в ОЗУ (режим записи) полученный результат. Причем возможно размещение в ОЗУ новых данных на местах прежних, которые в этом случае перестают существовать. Таким образом, ОЗУ может работать в режимах записи, считывания и хранения информации.

Постоянное ЗУ содержит информацию, которая не должна изменяться в ходе выполнения процессором программы. Такую информацию составляют стандартные подпрограммы, табличные данные, коды физических констант и постоянных коэффициентов и т. п. Эта информация заносится в ПЗУ предварительно, и в ходе работы процессора может только считываться. Таким образом ПЗУ работает в режимах хранения и считывания.

Функциональные возможности ОЗУ шире, чем ПЗУ: ОЗУ может работать в качестве ПЗУ, т. е. в режиме многократного считывания однократно записанной информации, а ПЗУ в качестве ОЗУ использовано быть не может, так как не позволяет в процессе работы изменить, занесенную в него информацию. В свою очередь, ПЗУ обладает преимуществом перед ОЗУ в свойстве сохранять информацию при сбоях и отключении питания. Это свойство получило название энергонезависимость. Оперативное ЗУ является энергозависимым, так как информация, записанная в ОЗУ, утрачивается при сбоях питания.

Для микросхем памяти, выпускаемых отечественной промышленностью, характерны широкая номенклатура типов, значительное , разнообразие вариантов конструктивно-технологического исполнения, большой диапазон функциональных характеристик и значений электрических параметров, существенные различия в режимах работы и в областях применения.

Микросхемы памяти изготавливают по полупроводниковой технологии на основе кремния с высокой степенью интеграции компонентов на кристалле, что определяет их принадлежность к большим интегральным схемам (БИС). Конструктивно БИС ‘памяти представляет собой полупроводниковый кристалл с площадью в несколько десятков квадратных миллиметров, заключенный в корпус.

–> ЧИТАТЬ ПОЛНОСТЬЮ <–

К-во Просмотров: 518

Бесплатно скачать Реферат: Блок памяти