Полупроводниковые диоды являются коммерчески доступными элементами электронных схем. Именно на них и строятся выпрямители. Номенклатура диодов чрезвычайно обширна. Для грамотного их использования в выпрямителях необходимо знать и понимать смысл их основных технических характеристик.

Ниже рассматриваются основные статические характеристики полупроводниковых диодов.

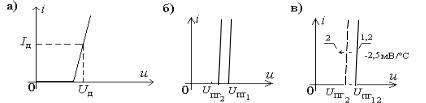

Пороговым напряжением Uпг называется такое значение напряжения на переходе, начиная с которого полупроводниковый диод проводит ток. При прямых напряжениях, меньших порогового, диод ток практически не проводит. Принято считать пороговым напряжение, равное 0,7В у кремниевых приборов и 0,3В – у германиевых. Как отмечалось выше, фактическое падение напряжения между выводами диода Uд всегда больше порогового Uпг, (рис. 10, а).

Укремниевых приборов фактическое падение напряжения составляет

1 В. Пороговое напряжение разнится от образца к образцу, даже у однотипных приборов (рис. 10, б). У дискретных диодов эта разница может достигать 0,1В. У диодов, изготавливаемых средствами интегральной технологии, она не превышает 0,01В. Поэтому прямые ветви вольтамперных характеристик полупроводниковых приборов не совпадают.

Пороговое напряжение полупроводниковых диодов зависит также и от температуры. Оно уменьшается со скоростью – 2,5 мВ/0С при повышении температуры перехода. Это значит, что если даже прямые ветви характеристик двух диодов первоначально совпадали (рис. 10, в), то при нагреве, например, диода 1 до температуры, превышающей температуру диода 2, прямая ветвь вольт-амперной характеристики 1-го диода сместится влево (пунктир на рис. 10, в).

Рис. 10

2.2. Номинальный ток

16

Под номинальным понимают максимальный постоянный ток, который может протекать через диод сколь угодно долго без разрушения прибора. Понятие номинального тока связано с понятием допустимой мощности рассеяния в диоде.

При протекании тока Iпр через прибор из-за конечного падения напряжения Uпр на нем, в приборе выделяется мощность Рв=UпрIпр. Это приводит к нагреву перехода, т. е. превышению его температуры Tп над температурой окружающей среды T0. Последнее обуславливает отток тепла от перехода в окружающую среду, то есть рассеяние мощности. Рассеяние мощности тем больше, чем выше температура перехода Tп по сравнению с температурой окружающей среды T0. Очевидно, что при Pв=const увеличение мощности рассеяния Pрас, обусловленное ростом температуры перехода может привести к тепловому равновесию Pв=Pрас, наблюдаемому при некоторой температуре перехода. Связь между мощностью рассеяния Pрас и перепадом температур T=Tп–T0 принимается линейной при небольших перепадах температур T. Эту связь принято записывать в виде соотношения T=RTPрас подобного закону Ома для резистивных электрических цепей. Коэффициент RТ называется термическим сопротивлением участка переход – среда. Определяется RТ практически площадью поверхности корпуса диода. Поскольку корпуса диодов унифицированы, то каждому конкретному типу диода соответствует вполне определенное значение RТ.

Как известно, температура p–n-переходов ограничивается некоторым допустимым значением Tп дп, превышение которого означает выход прибора из строя. Для кремниевых приборов Tп дп≈(175÷200)°С, а для герма-

ниевых Tп дп≈(125÷150)°С.

Отсюда следует, что при комнатной температуре, для каждого конкретного типа диода существует понятие допустимой мощности рассеяния

= Tпдп −T0 Pрас.дп(Tпдп) RТ .

Тем самым в условиях теплового равновесия ограничивается и выделяемая в приборе мощность:

|

P |

= P |

(T |

) = |

Tпдп −T0 |

. |

|

вдп |

рас.дп |

пдп |

RT |

||

С учетом приблизительного постоянства прямого падения напряжения на полупроводниковых диодах

Pвыд дп = Iд дпUп = Iд дп const ≈ Iд дп 1В = | Iд дп |.

17

Отсюда следует: Iддп = Tпдп −T0 . В силу постоянства Uп = 1В мощ-

RТ

ность, выделяющаяся в диоде, определяется средним током через диод.

Тогда Iд дп = Iср дп.

По этой причине средний ток через диод, оговариваемый в технической документации, является допустимым значением среднего тока при комнатной температуре. С увеличением температуры окружающей среды этот ток должен соответственно уменьшаться во избежание выхода диода из строя. Увеличение Iср дп возможно за счет уменьшения RТ. Это означает необходимость увеличения теплоотводящей поверхности диода, то есть добавления к нему теплоотвода.

Как следует из изложенного, Iср дп является мерой допустимой мощности рассеяния в диоде. Так диод со средним током в 1А в состоянии рассеять при комнатной температуре мощность, приблизительно равную 1 Вт.

Таким образом, для каждого конкретного типа прибора существует понятие тока, допустимого при комнатной температуре, превышение которого приводит к сгоранию диода. Номинальный ток, как ток, гарантирующий надежную эксплуатацию диода, выбирается меньше допустимого.

Номинальный ток через диод уменьшается с ростом температуры окружающей среды. Его можно и увеличивать посредством уменьшения RТ. Это достигается увеличением теплоотводящей поверхности диода – к корпусу диода присоединяют специальный конструктивный элемент называемый теплоотводом.

2.3. Пиковый (максимальный) ток

Пиковые или максимальные токи через диод могут существенно превышать их номинальные значения. Вопрос о пиковых токах более сложен, нежели о номинальных. Допустимые значения пиковых токов в диодах зависят не только от величин, но и длительности, а также от частоты их повторения. Так при частоте порядка 50 Гц пиковые токи длительностью 5 мс могут превышать номинальные в 10 – 20 раз. При уменьшении длительности до 2 мс импульсы токов могут превышать номинальный ток в 50 – 100 раз. Чаще всего фактические характеристики импульсных токов в электрических цепях трудно определимы. По этой причине лучше не допускать превышения их официальных допустимых значений.

2.4. Обратный ток диода

Обратный ток при комнатной температуре пренебрежимо мал в кремниевых приборах, но существенен в германиевых. К сожалению, этот ток

18

экспоненциально растет с ростом температуры перехода. Его можно грубо оценить формулой

Iо(T1) = Iо(T0) 2(T1−T0 )/10 ,

где Iо(T1) – обратный ток при температуре перехода T1; Iо(T0) – обратный ток, замеренный при температуре перехода T0. Естественно, что оценка тока по этой формуле тем достовернее, чем меньше T=T1–T0.

2.5. Обратное напряжение

Обратное напряжение Uоб, как техническая характеристика диода ставится в соответствие напряжению его пробоя. Естественно, оно меньше напряжения пробоя, ибо в режиме пробоя диод утрачивает свойство односторонней проводимости – перестает быть диодом. Обычно Uоб определяется с некоторым запасом.

Помимо перечисленных статических технических характеристик диода существуют еще и динамические. Наиболее существенные рассматриваются ниже.

2.6. Динамическое сопротивление диода

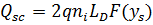

Поскольку при Uпр>0,1 В прямая ветвь вольт-амперной характеристики диода определяется соотношением (2), то динамическое сопротивление прибора – его сопротивление приращениям прямого тока через переход – может быть определено простой процедурой:

|

1 |

∂i |

1 |

U |

/ϕТ |

Iпр |

ϕ |

0,025В |

|||||||||||

|

= |

п |

= |

I |

0 |

e |

пр |

= |

или r = |

Т |

= |

. |

|||||||

|

r |

ϕ |

ϕ |

I |

I |

||||||||||||||

|

∂u |

п |

д |

пр |

пр |

||||||||||||||

|

д |

T |

Т |

2.7. Время выключения диода

Идеальный диод, включенный в цепь последовательно с резистивной нагрузкой (рис. 11, а) пропускает ток только в прямом направлении. При изменении знака напряжения в цепи Uц обратный ток через диод прекра-

щается (рис. 11, б и в).

В реальных полупроводниковых диодах размыкание цепи при мгновенном изменении знака напряжения цепи с прямого на обратный происходит не сразу. Дело в том, что при прохождении через кристалл прямой ток насыщает его основными носителями. Их концентрация в кристалле пропорциональна величине прямого тока. Для того чтобы диод разомкнул цепь, чтобы кристалл стал непроводящим, необходимо удалить основные носители тока из кристалла, т. е. создать обедненную зону на границе контакта слоев p и n-полупроводника. Этот процесс требует времени. В течение этого времени – времени рассасывания носителей tр – диод проводит ток в обратном направлении, так же как и в прямом (рис. 12).

19

|

а) |

б) |

U |

|||||

|

U ц |

t1 |

t2 |

|||||

|

U ц |

0 |

||||||

|

t |

|||||||

|

Rн |

Uн |

||||||

|

в) |

i |

||||||

|

U |

|||||||

|

R |

t1 |

t2 |

|||||

|

0 |

t |

||||||

Рис. 11

По окончании процесса рассасывания имеет место процесс медленного спада обратного тока через диод до значения I0 (рис. 12, а). Время рассасывания и время спада в сумме образуют время выключения диода. Время выключения диода tвыкл является технической характеристикой диода.

|

+U |

ц |

U |

|

0 |

t |

|

|

-U ц |

||

|

+U |

ц |

I |

|

Rн |

||

|

0 |

t |

|

|

tвкл |

||

|

-U ц |

tр |

|

|

Rн |

tвыкл

Рис. 12

20

Соседние файлы в папке metods

- #

- #

- #

- #

- #

- #

- #

- #

From Wikipedia, the free encyclopedia

Simulation result for formation of inversion channel (electron density) and attainment of threshold voltage (IV) in a nanowire MOSFET. Note that the y-axis is logarithmic, showing that only extremely small amounts of current pass below the threshold voltage (around 0.45 V) when the conducting channel connects.

The threshold voltage, commonly abbreviated as Vth or VGS(th), of a field-effect transistor (FET) is the minimum gate-to-source voltage (VGS) that is needed to create a conducting path between the source and drain terminals. It is an important scaling factor to maintain power efficiency.

When referring to a junction field-effect transistor (JFET), the threshold voltage is often called pinch-off voltage instead.[1][2] This is somewhat confusing since pinch off applied to insulated-gate field-effect transistor (IGFET) refers to the channel pinching that leads to current saturation behaviour under high source–drain bias, even though the current is never off. Unlike pinch off, the term threshold voltage is unambiguous and refers to the same concept in any field-effect transistor.

Basic principles[edit]

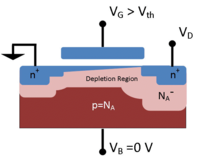

In n-channel enhancement-mode devices, a conductive channel does not exist naturally within the transistor, and a positive gate-to-source voltage is necessary to create one such. The positive voltage attracts free-floating electrons within the body towards the gate, forming a conductive channel. But first, enough electrons must be attracted near the gate to counter the dopant ions added to the body of the FET; this forms a region with no mobile carriers called a depletion region, and the voltage at which this occurs is the threshold voltage of the FET. Further gate-to-source voltage increase will attract even more electrons towards the gate which are able to create a conductive channel from source to drain; this process is called inversion. The reverse is true for the p-channel “enhancement-mode” MOS transistor. When VGS = 0 the device is “OFF” and the channel is open / non-conducting. The application of a negative gate voltage to the p-type “enhancement-mode” MOSFET enhances the channels conductivity turning it “ON”.

In contrast, n-channel depletion-mode devices have a conductive channel naturally existing within the transistor. Accordingly, the term threshold voltage does not readily apply to turning such devices on, but is used instead to denote the voltage level at which the channel is wide enough to allow electrons to flow easily. This ease-of-flow threshold also applies to p-channel depletion-mode devices, in which a negative voltage from gate to body/source creates a depletion layer by forcing the positively charged holes away from the gate-insulator/semiconductor interface, leaving exposed a carrier-free region of immobile, negatively charged acceptor ions.

For the n-channel depletion MOS transistor, a negative gate-source voltage will deplete (hence its name) the conductive channel of its free electrons switching the transistor “OFF”. Likewise for a p-channel “depletion-mode” MOS transistor a positive gate-source voltage will deplete the channel of its free holes, turning it “OFF”.

In wide planar transistors the threshold voltage is essentially independent of the drain–source voltage and is therefore a well defined characteristic, however it is less clear in modern nanometer-sized MOSFETs due to drain-induced barrier lowering.

Depletion region of an enhancement-mode nMOSFET biased below the threshold

Depletion region of an enhancement-mode nMOSFET biased above the threshold with channel formed

In the figures, the source (left side) and drain (right side) are labeled n+ to indicate heavily doped (blue) n-regions. The depletion layer dopant is labeled NA− to indicate that the ions in the (pink) depletion layer are negatively charged and there are very few holes. In the (red) bulk the number of holes p = NA making the bulk charge neutral.

If the gate voltage is below the threshold voltage (left figure), the “enhancement-mode” transistor is turned off and ideally there is no current from the drain to the source of the transistor. In fact, there is a current even for gate biases below the threshold (subthreshold leakage) current, although it is small and varies exponentially with gate bias. Therefore, datasheets will specify threshold voltage according to a specified measurable amount of current (commonly 250 μA or 1 mA).

If the gate voltage is above the threshold voltage (right figure), the “enhancement-mode” transistor is turned on, due to there being many electrons in the channel at the oxide-silicon interface, creating a low-resistance channel where charge can flow from drain to source. For voltages significantly above the threshold, this situation is called strong inversion. The channel is tapered when VD > 0 because the voltage drop due to the current in the resistive channel reduces the oxide field supporting the channel as the drain is approached.

Body effect[edit]

The body effect is the change in the threshold voltage by an amount approximately equal to the change in the source-bulk voltage,

For an enhancement-mode nMOS MOSFET, the body effect upon threshold voltage is computed according to the Shichman–Hodges model,[4] which is accurate for older process nodes,[clarification needed] using the following equation:

where;

Dependence on oxide thickness[edit]

In a given technology node, such as the 90-nm CMOS process, the threshold voltage depends on the choice of oxide and on oxide thickness. Using the body formulas above,

Thus, the thinner the oxide thickness, the lower the threshold voltage. Although this may seem to be an improvement, it is not without cost; because the thinner the oxide thickness, the higher the subthreshold leakage current through the device will be. Consequently, the design specification for 90-nm gate-oxide thickness was set at 1 nm to control the leakage current.[5] This kind of tunneling, called Fowler-Nordheim Tunneling.[6]

where;

Before scaling the design features down to 90 nm, a dual-oxide approach for creating the oxide thickness was a common solution to this issue. With a 90 nm process technology, a triple-oxide approach has been adopted in some cases.[7] One standard thin oxide is used for most transistors, another for I/O driver cells, and a third for memory-and-pass transistor cells. These differences are based purely on the characteristics of oxide thickness on threshold voltage of CMOS technologies.

Temperature dependence[edit]

As with the case of oxide thickness affecting threshold voltage, temperature has an effect on the threshold voltage of a CMOS device. Expanding on part of the equation in the body effect section

where;

We see that the surface potential has a direct relationship with the temperature. Looking above, that the threshold voltage does not have a direct relationship but is not independent of the effects. This variation is typically between −4 mV/K and −2 mV/K depending on doping level.[8] For a change of 30 °C this results in significant variation from the 500 mV design parameter commonly used for the 90-nm technology node.

Dependence on random dopant fluctuation[edit]

Random dopant fluctuation (RDF) is a form of process variation resulting from variation in the implanted impurity concentration. In MOSFET transistors, RDF in the channel region can alter the transistor’s properties, especially threshold voltage. In newer process technologies RDF has a larger effect because the total number of dopants is fewer.[9]

Research works are being carried out in order to suppress the dopant fluctuation which leads to the variation of threshold voltage between devices undergoing same manufacturing process.[10]

See also[edit]

- MOSFET operation

- Channel length modulation

- Multi-threshold CMOS

References[edit]

- ^ “Junction Field Effect Transistor (JFET)” (PDF). ETEE3212 Lecture Notes.

This is called the threshold, or pinch-off, voltage and occurs at vGS=VGS(OFF).

- ^ Sedra, Adel S.; Smith, Kenneth C. “5.11 THE JUNCTION FIELD-EFFECT TRANSISTOR (JFET)” (PDF). Microelectronic Circuits.

For JFETs the threshold voltage is called the pinch-off voltage and is denoted VP.

- ^ Marco Delaurenti, PhD dissertation, Design and optimization techniques of high-speed VLSI circuits (1999)) Archived 2014-11-10 at the Wayback Machine

- ^ NanoDotTek Report NDT14-08-2007, 12 August 2007

- ^ Sugii, Watanabe and Sugatani. Transistor Design for 90-nm Generation and Beyond. (2002)

- ^ S. M. Sze, Physics of Semiconductor Devices, Second Edition, New York: Wiley and Sons, 1981, pp. 496–504.

- ^ Anil Telikepalli, Xilinx Inc, Power considerations in designing with 90 nm FPGAs (2005))[1]

- ^ Weste and Eshraghian, Principles of CMOS VLSI Design : a systems perspective, Second Edition, (1993) pp.48 ISBN 0-201-53376-6

- ^ Asenov, A. Huang,Random dopant induced threshold voltage lowering and fluctuations in sub-0.1 μm MOSFET’s: A 3-D “atomistic” simulation study, Electron Devices, IEEE Transactions, 45, Issue: 12

- ^ Asenov, A. Huang,Suppression of random dopant-induced threshold voltage fluctuations in sub-0.1-μm MOSFET’s with epitaxial and δ-doped channels, Electron Devices, IEEE Transactions, 46, Issue: 8

External links[edit]

- Online lecture on: Threshold Voltage and MOSFET Capacitances by Dr. Lundstrom

Библиографическое описание:

Головяшкин, А. А. Расчет порогового напряжения МДП-структуры с учетом парциальных зарядов подвижных носителей заряда / А. А. Головяшкин, А. Н. Головяшкин. — Текст : непосредственный // Молодой ученый. — 2015. — № 4 (84). — С. 155-157. — URL: https://moluch.ru/archive/84/15649/ (дата обращения: 24.05.2023).

Для большинства элементов и приборов на основе МДП-структур одним из важнейших параметров является пороговое напряжение [1].

Точный расчет этого параметра затруднен в связи с неопределенностью значений встроенного заряда в диэлектрике и распределения поверхностных состояний на границе раздела диэлектрик — полупроводник. Поэтому для достижений расчетного значения используют подгонку параметра с помощью ионной имплантации [1]. Но одновременно с пороговым напряжением происходит изменение других параметров и характеристик структуры. Наиболее негативное влияние ионная имплантация оказывает на поверхностную подвижность носителей заряда, которая уменьшается с увеличением дозы. Это ухудшает функциональные возможности элементов. Снижение подвижности в МДП-транзисторе уменьшает крутизну передаточной характеристики, граничную рабочую частоту элемента, ухудшает статические и динамические характеристики. У приборов с зарядовой связью также возрастают потери информационного сигнала.

Снижение дозы ионной имплантации возможно за счет уточненного расчета значения порогового напряжения еще на ранних стадиях проектирования МДП-структуры. Для формирования структуры используют однородно легированную полупроводниковую подложку, поэтому достаточно рассмотреть одномерную модель.

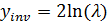

Производители элементной базы под пороговым напряжением понимают значение напряжения на затворе, при котором в МДП-транзисторе возникает так называемый предпороговый ток, не превышающий определенного минимального значения [2]. Более универсальным, особенного на стадии расчета, является значение напряжения затвора, при котором поверхностный потенциал полупроводника соответствует началу сильной инверсии поверхности. При начале инверсии поверхностные концентрации электронов и дырок равны: ps=ns=ni. При начале сильной инверсии поверхностная концентрация неосновных носителей равна значению объемной концентрации основных носителей заряда. Тогда падение напряжения Vsc на приповерхностной области объемного заряда (ПООЗ) полупроводника должно быть равно:

Vsc= (kT/q) ys = (kT/q) 2ln(λ), (1)

где k — постоянная Больцмана; T — температура по шкале Кельвина; q — заряд электрона по модулю; ys — поверхностный безразмерный потенциал, отсчитанный от положения собственного уровня Ферми в нейтральном объеме; λ = p0/ni = ni/n0 — степень (уровень) легирования.

Значение ys, которое определяется равенством (1), задает начало сильной инверсии (yinv).

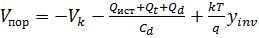

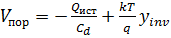

Теперь рассмотрим выражение для расчета порогового напряжения, которое часто используется в различных методиках и алгоритмах расчета:

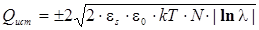

, (2)

, (2)

где Vk — контактная разность потенциалов, равная разности работ выхода электрона из полупроводника и металла; Qист — заряд ПОПЗ; Qt — эффективный заряд поверхностных состояний; Qd — эффективный встроенный заряд диэлектрика.

Для идеальной МДП структуры значения Vk, Qист и Qd равны нулю.

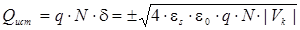

Совершенствование технологии производства позволили уменьшить влияние неконтролируемых зарядов и производить расчет по модели, которая учитывает только контактную разность потенциалов. Заряд Qист рассчитывался в приближении резкого p-n перехода:

,

,

и используя равенство (1) окончательно получаем:

, (3)

, (3)

где N — эффективная концентрация ионизированной примеси в полупроводниковой подложке, определяющая объемную концентрацию основных носителей заряда; ε0 –диэлектрическая постоянная; εs — относительная диэлектрическая проницаемость полупроводника [2–3].

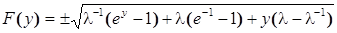

Для более корректного расчета порогового напряжения необходимо решить уравнение Пуассона с учетом заряда подвижных носителей. В результате первого интегрирования имеем следующее равенство:

, (4)

, (4)

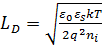

и для полупроводника в равновесном состоянии:  , (5)

, (5)

где  — длина Дебая собственного полупроводника.

— длина Дебая собственного полупроводника.

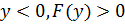

Правило знаков для F(y) следующее: при  , и наоборот.

, и наоборот.

Из уравнения (4) очевидно, что функция F(y) есть напряжённость электрического поля в ПООЗ с точностью до множителя kT/q. Используя теорему Гаусса, получим выражение для расчета поверхностной плотности заряда на границе полупроводник — диэлектрик:

. (6)

. (6)

Для расчета порогового напряжения через  необходимо задать значение ys в выражениях (5–6) равным

необходимо задать значение ys в выражениях (5–6) равным  и заменить в выражение (2) Qист на

и заменить в выражение (2) Qист на  .

.

Теперь оценим, насколько оправдано предложенное усложнение. Для идеальной структуры Vk, Qd и Qt равны нулю. Тогда:

. (7)

. (7)

Для расчета возьмем типовые значения параметров кремниевых интегральных МОП — транзисторов при температуре 300К: толщина окисла 20 нм, λ = 103…105 [1, 4]. Результаты приведены в таблице 1.

Таблица 1

Абсолютная  и относительная

и относительная  погрешности расчета порогового напряжения

погрешности расчета порогового напряжения

|

Параметр легирования λ |

|

|

|

1013 |

76 |

10,75 |

|

1015 |

5,6 |

0,34 |

Для высокоомных подложек погрешность расчета является наиболее существенной.

Если в выражении (2) учитывать все факторы, определяющие пороговое напряжение реальной МДП- структуры, то относительная погрешность расчета может уменьшиться, но абсолютное значение останется прежним. А именно абсолютное значение определяет дозу ионной имплантации области канала для подгонки значения  .

.

Кроме того, значение абсолютной погрешности соизмеримо со слагаемыми значения напряжения плоских зон, которые определяются величинами Qt, Qd. Это означает, что при экспериментальных исследованиях этих параметров результаты и их интерпретация становятся недостоверными. Поэтому невозможно при испытаниях тестовых образцов установить истинную причину отклонения расчетных значений от экспериментальных. Усложняется и контроль технологических режимов процессов формирования МДП- структур [4]. При чем, в открытых алгоритмах САПР до сих пор используется выражение (2) [5]. Следовательно, при применении САПР для расчета и проектирования МДП — элементов желательно «перепроверить» вычисления порогового напряжения заменяя в выражение (6) Qист на  .

.

Литература:

1. Рабаи, Жан М., Чандраскан, Ананта, Николич, Боривож. Цифровые интегральные схемы. 2-е издание.: Пер. с англ. — М: ООО «И. Д. Вильямс», 2007. — 912 с.

2. http://www.elek.oglib.ru/bgl/4192/323.html

3. http://dssp.petrsu.ru/book/chapter6/part11.shtml

4. lib.yar.ru/yarcln/edoc/yarsu/pdf/190200.pdf

5. www.rodnik.ru/product/sapr/edaexpress/

Основные термины (генерируются автоматически): пороговое напряжение, ионная имплантация, абсолютное значение, выражение, значение напряжения, контактная разность потенциалов, объемная концентрация, основной носитель заряда, погрешность расчета, сильная инверсия.

Igor Gosudarev

Оракул

(61833)

14 лет назад

p-n переход диода “открывается”, начиная с определенного напряжения.

Обычно 100-500 мВ.

Причину сего пояснять долго.

см. комментарий.

Igor GosudarevОракул (61833)

14 лет назад

Кратко.

n-облсть легирована донорами

p-область – акцепторами.

При создании p-n перехода часть электронов из n-обл. под действием nkT переходит в p-обл., тем самым заряжая ее отрицательно, а n-обл. заряжается положительно. Процесс идет до тех пор, пока возникшее напряжение на p-n переходе соим эл.полем не остановит его. Переход, в результате, в исходном состоянии имеет “обратное смещение”.

Ток через диод начинает протекать после того, как приложенное прямое напряжение превысит это “обратное смещение”.

Председатель

Искусственный Интеллект

(230080)

14 лет назад

Плоский атом (Flat Atom) — новая квантовая атомоподобная структура, что индуцируется в однородном электрическом поле МДП- транзисторов. Впервые описана в средине 90-х годов Якимахой. Известно, что в природе встречаются только сферически симметричные атомы (объемные структуры) , теория которых была разработана в 20-х годах прошлого столетия путем введения новой физической дисциплины, которая получила название квантовая механика, в основе которой лежит уравнение Шредингера. В начале 90-х годов прошлого столетия была открыта атомоподобная структура в МДП- транзисторах, что проявляла себя в форме низкочастотного резананса обусловленного малыми значеннями реактивных квантовых параметров. Квантовалась плоская плоскость, емкость, частота и энергия :

F

m

rad/S

,

где , — масса покоя электрона и — радиус Бора. В случае заполнения кванта плоской плоскости одним электроном, эта энергия была в раз меньше за боровский масштаб энергий. Но в отличие от сферически симметричного атома Бора, плоский атом есть чисто статистическое явление, и поэтому квант плоскости здесь может заполняться многими электронами. Например, полное заполнение первого уровня энергии плоского атома осуществляется большой численностью электронов:

Содержание [убрать]

1 Плоский атом как резонансный контур

2 Проявления плоского атома через ВАХ МДП-транзистора

3 См. также

4 Литература

[править] Плоский атом как резонансный контур

Так само, как и в случае атома Бора, плоский резонансный контур имеет квант плоской индуктивности:

H.

Элементарная теория в рамках которой определяется реактивные параметры подана в статье, посвященной квантовому эффетку Шоттки. Последние и определяют волновое сопротивление контура:

,

равное волновому сопротивлению вакуума, а его резонансеая частота ω0 определяет масштаб энергий одноэлектронного плоского атома.

[править] Проявления плоского атома через ВАХ МДП-транзистора

Необходимо отметить, что электроны связанные с реактивными квантовыми параметрами, очевидно связаны, и не принимают участия в создании тока стока МДП-транзистора. Поэтому они могут себя проявить только в изменении пороговых напряжений и параметров, связанных с низкочастотным резонансом.

Формирование квантового плоского атома состоит из постоянного заполнение уровней энергии многочисленными электронами. Режим слабой инверсии МДП-транзистора можно интерпретировать как режим заполнения первого уровня энергии электронами. С началом заполнения второго уровня энергии начинается режим т. н. сильной инверсии.

Необходимо отметить, что при этом напряжения на затворе разбиваются равномерно на области около 1,2В, при чем для каждой области имеем свое пороговое напряжение. Через пороговое напряжение и выражается перманентно изменения зарядов на кванте плоскости . Изломы сток-затворной характеристики с периодом 1,2В можна определить путем подачи переменного напряжения малой амплитуды на затвор (т. н. спектроскопические исследования МДП- транзисторов, связанные с измерениями производных старших порядков) .

Источник: ВИКИПЕДИЯ

Andre

Мастер

(2309)

14 лет назад

В прямом направлении диод также всегда закрыт. И открывается при приложении прямого напряжения выше порогового значения. Оно обычно не большое – несколько милливольт, но существует. А обратное пороговое напряжение для диода – это максимальное напряжение пробоя его перехода и обычно измеряется десятками, сотнями или тысячами вольт.

Jessie

Профи

(804)

14 лет назад

Пороговое напряжение – это напряжение, начиная с которого увеличение прямого падение напряжения от тока приобретает линейную зависимость, которая определяется значением динамического сопротивления диода. Ниже этого напряжения диод “закрыт”

Вольный ветер

Искусственный Интеллект

(283261)

2 года назад

Берем батарейку 1,5 вольта измеряем на ней напряжение смотрим, 1,52 к примеру, измеряем снова, но через любой диод смотрим 1,02 – пол вольта диод украл, это и есть его пороговое напряжение когда он закрыт, а когда отрыт на нем падает от 0,2, до 0,7 вольта, зависит от типа диода….

Расчет порогового напряжения

В связи с тем, что управляющий и нагрузочный транзисторы создаются в едином технологическом процессе, а пороговое напряжение определяется уровнем легирования подложки и характеристиками подзатворного элемента, величина порогового напряжения оказывается одинаковой как для управляющего, так и для нагрузочного транзистора.

Найдем емкость подзатворного диэлектрика:

Найдем объемный потенциал Ферми по формуле:

Напряжение прокола:

Расчет выходных характеристик.

а) таблица токов насыщения при различных значениях напряжения на затворе управляющего транзистора:

Ток насыщения:

Введем величину:

Значения UG: 1,89 В; 2,52 В; 3,16 В; 3,79 В

|

UG, В |

1,89 |

2,52 |

3,16 |

3,79 |

1,25 |

|

Iнас, мА |

0,28 |

1,11 |

2,51 |

4,46 |

0,00 |

б) Вольт-амперная характеристика управляющего транзистора в крутой линейной части:

Ток стока

где UDS=Uвых – напряжение исток-сток

Введем величину:

При , При

|

UDS, В |

0,10 |

0,15 |

0,20 |

0,25 |

|

ID, мА |

0,09 |

0,13 |

0,18 |

0,22 |

При

|

UDS, В |

0,15 |

0,30 |

0,45 |

0,60 |

|

ID, мА |

0,27 |

0,53 |

0,80 |

1,06 |

При

|

UDS, В |

0,25 |

0,45 |

0,70 |

0,90 |

|

ID, мА |

0,66 |

1,19 |

1,86 |

2,39 |

При

|

UDS, В |

0,30 |

0,60 |

0,90 |

1,25 |

|

ID, мА |

1,06 |

2,12 |

3,18 |

4,42 |

Для области насыщения:

Транзисторы в качестве нагрузочного элемента.

Ток стока:

где – напряжение на нагрузочном транзисторе, затвор соединен со стоком.

Введем величину:

Находим для нескольких значений , а через –

Пусть

Подставим значения в формулу, выразим

|

ID, мА |

0,1 |

0,2 |

0,3 |

0,4 |

|

Uвых, В |

2,47 |

1,70 |

0,93 |

0,16 |

Передаточная характеристика инвертора.

Для построения передаточной характеристики графически решается зависимость

,

Время переключения инвертора

Критерий сильного поля

где – скорость звука

Напряженность в канале:

,

Условия сильного поля в канале выполняются.

Вычисление скорости насыщения:

транзистор металлооксидный пленка инвертор

где – максимальная энергия оптического фотона

колебаний решетки Si.

– эффективная масса носителя

– масса электрона

где – продольная эффективная масса электрона

– поперечная эффективная масса электрона

Т.к.

Время пролета канала

Это время внутренней реакции необходимо сравнивать с временами заряда-разряда емкостей.

Время заряда емкости (нагрузки) при запертом управляющем транзисторе:

Крутизна нагрузочного транзистора в области насыщения:

Время разряда нагрузочной емкости через открывающийся управляющий транзистор:

Максимальное время задержки – время заряда –

При цитировании материалов в рефератах, курсовых, дипломных работах правильно указывайте источник цитирования, для удобства можете скопировать из поля ниже: