В

качестве основных характеристик

микропроцессоров используют тактовую

частоту, архитектуру ядра и количество

ядер, технологический процесс производства,

частоту системной шины, размер кэша,

параметры энергоэффективности и

поддерживаемые технологии. Все эти

характеристики, так или иначе, определяют

самую главную характеристику любого

процессора ‑ его производительность.

1.2.1 Тактовая частота

До

недавнего времени тактовая частота

процессора напрямую связывалась с его

производительностью, то есть чем выше

тактовая частота процессора, тем он

производительнее. Собственно, сама

архитектура NetBurst,

положенная в основу процессоров Intel

Pentium 4,

изначально была ориентирована на то,

что основным средством увеличения

производительности процессоров будет

рост тактовой частоты. Действительно,

за время существования процессоров

Intel

Pentium 4

их тактовая частота была увеличена во

много раз. Конечно, увеличение тактовой

частоты – это далеко не единственное

нововведение, которое сопутствовало

появлению новых процессоров семейства

Intel

Pentium 4.

В то же время можно сказать, что для

процессора Pentium 4

повышение тактовой частоты являлось

одним из основных способов увеличения

его производительности. Однако и

потребители, и разработчики могут сейчас

убедиться в том, что подобная «гигагерцевая

гонка» не стала оптимальным способом

увеличения мощности. Зависимость между

тактовой частотой процессора и его

производительностью достаточно простая.

Производительность процессора принято

отождествлять со скоростью выполнения

им инструкций программного кода; таким

образом, производительность – это

количество инструкций, выполняемых

процессором в единицу времени:

Переписав

это выражение в виде произведения

количества инструкций, выполняемых за

один такт процессора (Instruction

Per

Clock,

IPC),

на количество тактов процессора за

единицу времени (тактовая частота

процессора, ):

получаем, что

производительность процессора прямо

пропорциональна его тактовой частоте.

1.2.2 Архитектура процессора

Из

приведенной формулы вытекает, что, кроме

тактовой частоты, производительность

процессора зависит и от количества

инструкций, выполняемых за один такт

процессора, которое, в свою очередь,

определяется архитектурой процессора,

то есть от количества исполняемых

блоков, от длины конвейера и от

эффективности его заполнения, от блока

предвыборки и т. д. Кроме того, естественно,

существует также зависимость от

оптимизации программного кода к данной

архитектуре процессора.

В

результате того, что основные производители

(Intel

и AMD)

столкнулись со значительными трудностями

на пути увеличения тактовых частот, как

процессорных ядер, так и шин передачи

данных, а пользователи и разработчики

программного обеспечения по-прежнему

требовали увеличения мощности систем,

пришлось искать другие выходы из

сложившегося положения.

В

этом свете наиболее перспективным

решением стало увеличение количества

ядер микропроцессора. Следует сказать,

что подобная идея впервые пришла на ум

«голубому гиганту» (IBM)

еще в далеком 1999 году, когда он представил

опытный образец двуядерного Power4,

а в 2001 году совместно с Apple

уже вовсю торговал готовыми решениями.

Производители

процессоров для платформы х86 спустя

год после этого события (2002) заявили о

своих намерениях развивать многоядерную

архитектуру микропроцессоров. Стремясь

подтвердить свой статус лидера отрасли,

компания Intel

первой выпустила подобный чип в марте

2005 года. Ее главный конкурент, AMD,

отстав всего на три дня, представил

полную линейку серверных двуядерных

процессоров Opteron,

анонсировал двуядерные процессоры

Athlon 64 Х2

для настольных систем и начал поставки

Opteron

8xx.

Апофеозом

противостояния двух ведущих компаний

стал момент выхода на рынок продуктов

Intel Core 2.

Это событие датируется 27 июля 2006 года,

что не только изменило расстановку сил

на рынке, но и коренным образом повлияло

на критерии оценки производительности.

Маркетологи

из Intel

предложили вместо тактовой частоты

оперировать категориями энергоэффективности.

В этом свете ключевым параметром стала

оптимальная производительность, которая

отражает количество энергии, затрачиваемой

процессором на выполнение определенного

набора инструкций.

Рассмотрим

формулу, предложенную Intel,

более детально. Производительность

(Performance)

определяется как произведение тактовой

частоты процессора (Frequency)

на величину IPC,

определяющую количество инструкций,

исполняемых CPU

за один такт:

.

Получается, что

увеличить быстродействие можно двумя

способами: поднимая частоту и/или

увеличивая количество инструкций,

выполняемых за один такт.

Параметр

Frequency

зависит от технических характеристик

процессора. Для конкретного экземпляра

процессора частоту можно увеличить

сверх номинала, подняв напряжение и не

забыв при этом поставить более мощную

систему охлаждения.

В

свою очередь, второй аргумент формулы

зависит от логической структуры

процессорного ядра: количества декодеров

инструкций и количества вычислительных

блоков. Функциональные особенности

каждого из этих узлов играют не менее,

важную роль, чем их количество. В

частности, повышение производительности

процессора возможно за счет уменьшения

числа операций для обработки одного и

того же объема данных. Типичным примером

является внедрение SIMD-команд,

таких как 3DNow!,

SSE,

SSE2,

SSE3

и SSE4.

Что

же касается энергопотребления, то оно

вычисляется как произведение тактовой

частоты процессора на квадрат напряжения

U,

при

котором функционирует процессорное

ядро, и некую величину Cdynamic

(динамическая емкость), определяемую

архитектурой процессора и зависящую

от количества транзисторов и их активности

во время работы процессора:

.

Из

этих двух формул вытекает следующее

соотношение, определяющее энергоэффективность

процессора:

Из

него следует, что для получения наилучшего

показателя производителям необходимо

работать над оптимизацией архитектуры

с целью улучшения функциональности

исполнительных блоков, при этом, не

допуская чрезмерного увеличения

динамической емкости.

Как

мы уже вскользь упоминали, напряжение

питания ядра, также оказывающее влияние

на соотношение производительности и

энергопотребления, зависит не столько

от архитектуры, сколько от технологических

особенностей изготовления процессора.

В этом легко убедиться, сравнив два

процессора с одним и тем же индексом,

но произведенных по различным техпроцессам.

Что

касается тактовой частоты, то, как

показывают наши выкладки, на рассматриваемое

соотношение она вообще не влияет.

Поэтому, сделав такой элегантный ход

конем, Intel

вышла из гонки, не только сохранив

репутацию, но и озадачив при этом AMD,

чьи изделия на тот момент также были

довольно «горячи».

На

первый взгляд все эти формулы и логические

выкладки от Intel

весьма перспективны, однако подобный

подход в оценке эффективности не является

самым оптимальным, ведь замечательными

показателями энергоэффективности при

желании смогут похвастаться и маломощные

процессоры.

В

свете сомнительной формулы от Intel

главный конкурент в долгу не остался.

В своей инновационной разработке под

кодовым именем Fusion

инженеры из AMD

предложили пойти еще дальше и оценивать

продукт по формуле «операция на ватт и

на доллар».

В

частности, концепция Fusion

предполагает объединение ядер различного

назначения в одном чипе. Каждое из них

(или каждая из групп ядер) будет обращаться

к собственной кэш-памяти, а в качестве

связующей шины выступит HyperTransport.

Процессоры Fusion

будут напрямую обращаться к системной

памяти, разделяемой между нуждами

центральной и графической частей

процессора. Вероятно, даже техпроцесс

изготовления CPU

и GPU

будет различаться.

Соседние файлы в предмете [НЕСОРТИРОВАННОЕ]

- #

- #

- #

- #

- #

- #

- #

- #

- #

- #

- #

Задание №1

Рассмотрите вопросы, связанные с принципом построения цифровых систем передачи ЦСП с ВРК ИКМ-ВД.

-

Составьте структурную схему, поясняющую принцип построения ЦСП с ИКМ-ВД для заданного числа телефонных каналов. Кратко укажите назначение всех узлов и этапы аналого-цифрового преобразования АЦП в тракте передачи и цифро-аналогового преобразования ЦАП в тракте приема.

-

Рассчитайте тактовую частоту fт, длительность канального интервала Тки, длительность цикла Ти, длительность сверхцикла Тсц.

-

Постройте диаграмму временного цикла, сверхцикла, канального интервала, разрядного интервала.

-

Заполните рисунок 1 по мере выполнения заданий 2, 3, 4, 5 данной домашней работы.

Исходные данные:

|

Число ТЛФ каналов |

Fg, кГц |

m |

Передача СУВ |

|

18 |

8 |

8 |

За один цикл передаются СУВ для двух ТЛФ каналов |

-

3 этапа аналого-цифрового преобразования АЦП на передаче:

-

Дискретизация по времени;

-

Квантование по уровню;

-

Кодирование.

-

Назначение узлов схемы:

ФНЧ передачи – фильтр нижних частот – выделение ограниченного спектра частот из сигнала;

М – канальный амплитудно-импульсный модулятор – осуществляет дискретизацию передаваемых сигналов во времени;

ГОпр и ГОпер – генераторное оборудование – посылает канальные импульсы для управления модуляторами, на передаче и приеме СУВ для дискретизации сигналов управления и взаимодействия, обеспечивает правильный порядок следования циклов в сверхцикле и кодовых групп в цикле передачи и приема;

ЗГ – задающий генератор – формирует гармоничный высокостабильный сигнал с частотой равной или кратной fт;

ВТЧ – выделитель тактовой частоты – для синхронной и синфазной работы ГО;

Пер СУВ – передатчик сигналов управления и взаимодействия – дискретизация СУВ, передаваемых по телефонным каналам для управления приборами АТС,

Пер СС – передатчик синхросигнала – для передачи синхросигнала цикловой синхронизации;

Кодер – преобразование амплитуды АИМ сигнала в 8-ми разрядную кодовую комбинацию, квантование по уровню и кодирование;

УО – устройство объединения – объединение кодовых групп каналов выхода кодера, кодирование сигналов СУВ и кодовой группы синхросигнала в циклы и сверхциклы;

ПК пер – преобразователь кода передачи – преобразование однополярного ИКМ сигнала в биполярный сигнал, удобный для передачи по линейному тракту;

РЛ – линейный регенератор – для периодического восстановления ИКМ сигнала в процессе передачи по линии связи;

РС – станционный регенератор – восстановление ИКМ сигнала на приемной станции;

ПК пр – преобразователь кода – преобразует биполярный сигнал в однополярный;

Пр СС – приемник синхросигналов – правильное декодирование и распределение сигналов по своим телефонным каналам и каналам передачи СУВ;

УР – устройство разделения – разделяет кодовые группы ТЛФ каналов и СУВ;

Пр СУВ – приемник групповых сигналов управления и взаимодействия – распределяет СУВ по своим каналам;

Декодер – преобразует групповой ИКМ сигнал в групповой АИМ сигнал; для преобразования 8-ми разрядной кодовой комбинации в амплитуду КАИМ сигнала;

ВС – временной селектор – обеспечивает выделение отсчетов своего канал из группового АИМ сигнала;

ФНЧ приема – восстановление непрерывного исходного сигнала из последовательности его АИМ отсчетов.

Тактовая частота рассчитывается по формуле:

Fт=Fд×m×Nки, (кГц), где Fд =8 кГц – частота дискретизации ТЛФ сигнала; m=8 – разрядность кодовой комбинации; Nки – число канальных интервалов в цикле системы; складывается из числа ТЛФ каналов, одного канального интервала для системы синхронизации и одного КИ для передачи сигналов управления и взаимодействия между АТС СУВ.

FТ=8×(18+2) ×8×103=1280 (кГц).

Длительность тактового (разрядного) интервала рассчитывается по формуле:

Тт= , мкс

Тт= =0,781 (мкс).

Длительность импульса рассчитывается по формуле:

τ= , мкс

τ= =0,39 (мкс).

Длительность канального интервала рассчитывается по формуле:

Тки= Тт×m, мкс

Тки=0,781×8=6,248 (мкс).

Длительность цикла рассчитывается по формуле:

Тц=Тки×Nки, мкс

Тц=6,248 ×20=124,96 (мкс).

Длительность сверхцикла рассчитывается по формуле:

S= +1

S= +1=10.

Диаграмма временных цикла, сверхцикла, канального интервала и разрядного интервала:

4. Упрощенная структурная схема ЦСП с ИКМ-ВД: см. приложение №1.

Задание №2

-

Составьте схему построения генераторного оборудования ГОпер или ГОпр для заданного числа ТЛФ каналов. Укажите назначение элементов схемы.

-

Укажите отличие ГОпер от ГОпр; с помощью чего обеспечивается синхронная и синфазная работа ГОпер и ГОпр; назначение сигналов «Установка по циклу» и «Установка по сверхциклу».

-

Рассчитайте частоты импульсных последовательностей, управляющих работой АИМ или временных селекторов ВС, кодера или декодера, передатчика или приемника СУВ.

-

Рассчитанные значения Fт, Fк, Fр, Fц проставьте на упрощенной структурной схеме ЦСП с ИКМ-ВД.

Исходные данные:

|

ГО |

Число ТЛФ каналов |

Число канальных интервалов, Nки |

Число циклов в сверхцикле, S |

|

ГОпер |

18 |

20 |

10 |

1. Структурная схема ГО передачи:

Назначение элементов схемы:

ЗГ – задающий генератор – формирует гармоничный высокостабильный сигнал с частотой равной или кратной fт;

ФТП – формирователь тактовой последовательности – вырабатывает основную импульсную последовательность с частотой следования fт;

РР – распределитель разрядный – формирует m импульсных последовательностей. Число разрядных импульсов, формирующих РР, равно числу разрядов в кодовой комбинации;

РК – распределитель канальный – формирует управляющие канальные импульсные последовательности КИ0, КИ1, …, КИn, где n – число канальных интервалов в цикле;

РЦ – распределитель цикловой – формирует цикловые импульсные последовательности Ц0, Ц1, …, ЦS, где s – число циклов в сверхцикле.

В соответствии с рекомендациями МККТТ относительная нестабильность частоты ЗГ должна быть не хуже 10-5, поэтому в ЗГ используется кварцевая стабилизация частоты.

2. В отличие от ГОпер, в ГОпр используется выделитель тактовой частоты системы устройств тактовой синхронизации (для обеспечения синхронной и синфазной работы передающей и приемной станции).

Для подстройки генераторного оборудования по циклам и сверхциклам используются сигналы «Установка по циклу» и «Установка по сверхциклу». Это дает возможность подстраивать ГО одной станции в режим цикловой и сверхцикловой синхронизации с ГО другой станции.

Тактовая частота рассчитывается по формуле:

Fт=Fд×m×Nки, кГц

Fт=8×(18+2) ×8×103=1280 (кГц).

Частота следования разрядных импульсов рассчитывается по формуле:

Fр= , кГц, где m – число разрядов в кодовой комбинации

Fр= =160 (кГц).

Частота следования канальных импульсных последовательностей (частота дискретизации) рассчитывается по формуле:

Fк=Fд= , кГц, где Nku – число канальных интервалов в цикле передачи

Fк=Fд= =8 (кГц).

Частота следования цикловых импульсных последовательностей рассчитывается по формуле:

Fц= , Гц, где S – число циклов в сверхцикле

Fц= =800 (Гц).

Задание №3.

-

Начертите структурную схему нелинейного кодера. Кратко поясните: 3 этапа кодирования, назначение всех узлов кодера.

-

выполните операцию нелинейного кодирования. Рассчитайте ошибку квантования.

-

На упрощенной структурной схеме ЦСП с ИКМ-ВД на выходе кодера приведите полученную в результате кодирования кодовую 8-разрядную комбинацию.

Для кодирования используется нелинейный кодер взвешивающего типа с характеристикой компрессии А – 87,6/13.

Значение амплитуды отсчета АИМ-сигнала в у. е. – «+130».

1. Назначение кодера – для преобразования амплитуды отсчета АИМ-сигнала в соответствующую 8-разрядную кодовую комбинацию.

3 этапа кодирования:

-

Кодирование полярности (результат записывается в первом разряде);

-

Кодирование номера сегмента, выбор основного эталонного тока (результат записывается во 2, 3, 4 разрядах;

-

Кодирование уровня квантования внутри выбранного сегмента, выбор дополнительного эталонного тока (результат записывается в 5, 6, 7, 8 разрядах).

Назначение элементов схемы:

Компаратор определяет знак разности между амплитудами токов кодируемого отсчета и эталона (Ic и Iэт);

Цифровой регистр служит для записи решений компаратора после каждого такта кодирования и формирования структуры кодовой группы;

Генератор эталонов (ГЭТ(+) и ГЭТ()) формирует полярность и величины эталонов, количество формируемых эталонов равно 11, их значения – 1, 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024 усл. ед.

ПК преобразует параллельный код в последовательный, считывая состояние выходов 1 … 8 ЦР;

ГОпер управляет работой узлов кодера;

БКЭ – блок выбора и коммутации эталонных токов – для подключения выбранных ГЭТ, а также для подключения выбранных эталонных токов по сигналам от ключей;

КЛ – компрессирующая логика – для коммутации поступающего от ЦР семиразрядного регистра (без первого символа полярности) в П-разрядный двоичный код для управления разрядами выбранного ГЭТ.

Структурная схема нелинейного кодера: см. приложение №2.

1-й этап – кодирование полярности – 130>0 → 1;

2-й этап – кодирование номера сегмента, выбор основного эталонного тока –

|

130>128 → 1 130<512 → 0 130<256 → 0 |

→ 4 сегмент (ОЭ для 4 сегмента – 128) |

3-й этап – кодирование уровня квантования внутри выбранного сегмента, выбор дополнительного эталонного тока: ОЭ –128, ДЭ –64, 32, 16, 8

130<128+64 → 0

130<128+32 → 0

130<128+16 → 0

130<128+8 → 0

Шаг квантования равен последнему эталону – 8

Ошибка квантования: εкв=130–128=2, не должна превышать 0,5Δ

|

Опред. полярности |

Выбор основного эталонного тока, Iосн.эт. |

Вкл. Iосн.эт. |

Дополнительные эталонные токи, Iдоп.эт. |

||||||

|

Разряды кодирования |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

|

|

Iэт. |

1 |

128 |

512 |

256 |

128 |

64 |

32 |

16 |

8 |

|

Iаим Σ Iэт. |

130>0 |

130128>0 |

130–512<0 |

130–256<0 |

130 – (128 +64) <0 |

130 – (128+32) <0 |

130 – (128+16) <0 |

130 – (128+8) <0 |

|

|

Состояние выхода компаратора |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

Запись решения в ЦР |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

Шаг квантования |

8 |

||||||||

|

Ошибка квантования, |

2 |

||||||||

|

1-й этап |

2-й этап |

3-й этап |

При неравномерном квантовании шаг квантования изменяется в допустимых пределах амплитудных значений квантуемых сигналов, возрастая с увеличением уровня сигнала. Абсолютная ошибка квантования возрастает с увеличением уровня сигнала, но ее относительное значение, т.е. отношение сигнал-ошибка квантования, не изменяется. Использование неравномерного квантования позволяет выровнять отношение сигнал-ошибка квантования во всем диапазоне сигналов, а, следовательно, сократить число шагов квантования в 2 … 4 раза по сравнению с равномерным квантованием до Мкв.=128 … 256, что требует семи разрядов кодовой группы.

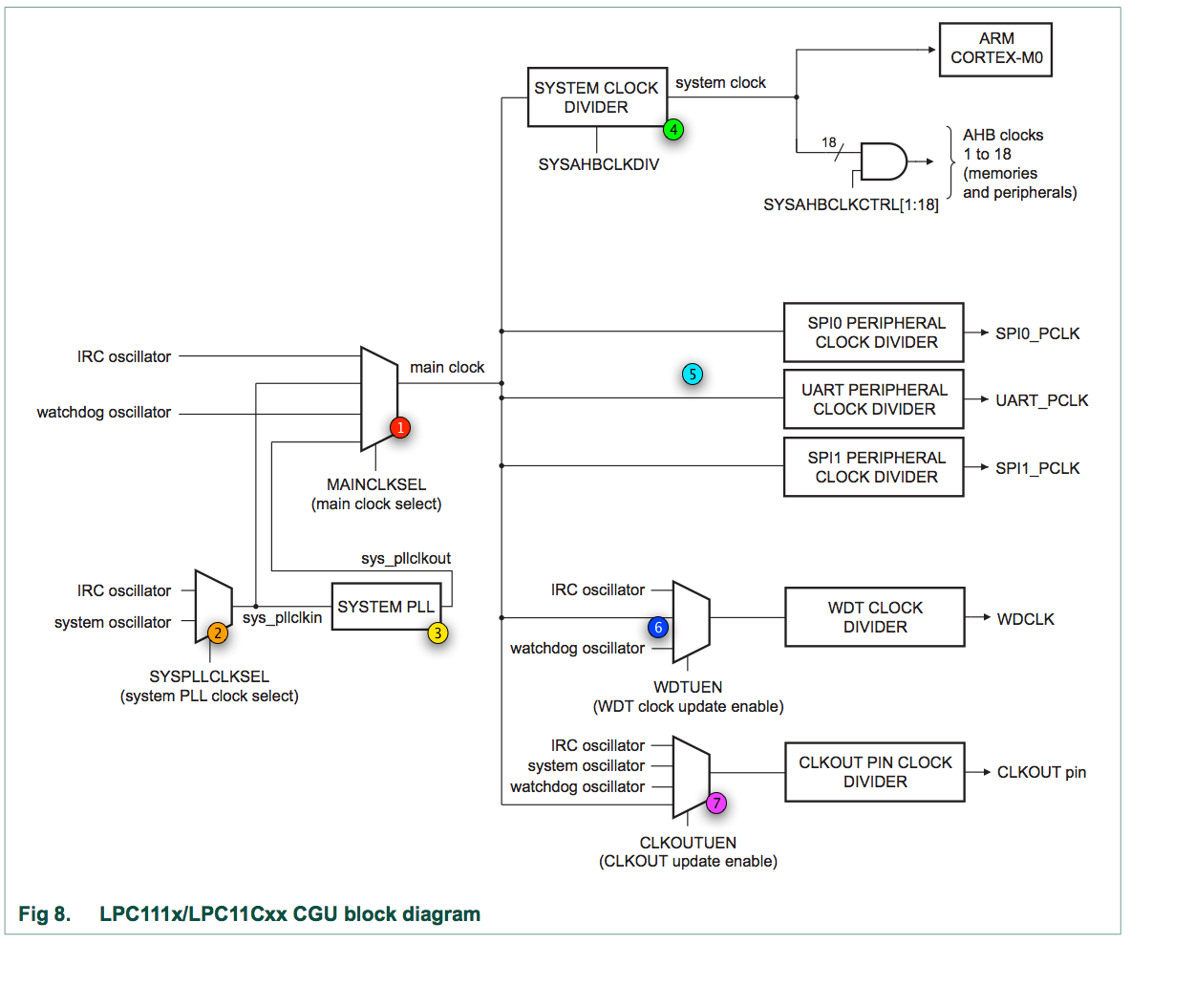

Сегодня мы разберемся с двумя важными вопросами: как писать более эффективный код с CMSIS и как правильно рассчитывать скорость работы процессора. Начнем мы со второй части и изучим процессы, которые происходят в LPC1114 для генерации тактовой частоты.

Тактовая частота – основной источник «рабочей силы» в процессоре, ее генератор можно сравнить с сердцем у человека. В разных компонентах процессора может использоваться разная частота, которая, тем не менее, зарождается обычно в одном и том же кристалле (или резонаторе).

Большинство процессоров имеют встроенный резонатор и возможность подключить внешний резонатор или кристалл. Зачем это сделано? В основном, для удешевления процессора. Встроенный резонатор типично имеет погрешность около 1%, чего может хватить для многих задач, но есть еще больше задач, для которых такая точность неприемлема. В самом деле, если мы будем, например, считать время на встроенном резонаторе, то погрешность за сутки может достигнуть 14 минут. Если вы передаете пакет по сети где-то раз в полчаса – это совершенно не критичная погрешность. Другое дело, если вы делаете будильник.

(изображение из LPC111x User Manual)

Выше представлена обзорная схема генератора тактовой частоты, разбитая на компоненты. Сейчас мы займемся каждым из них по отдельности.

⓵ Основная частота

MAINCLKSEL задает основную частоту, от которой зависят почти все остальные. Она может быть основана на одном из нескольких источников.

Во-первых, это IRC – внутренний резонатор. Рабочая частота – 12 МГц (на самом деле, можно тюнинговать в небольших пределах), погрешность — около 1%. Именно отсюда генерируется тактовая частота процессора в момент старта, так что весь загрузочный код выполняется при тактовой частоте в 12 МГц. Вариант максимально простой (вам вообще ничего не надо делать, чтобы он работал), не требует дополнительных внешних компонентов. К сожалению, имеет свои проблемы: резонатор, как я уже упоминал, несколько неточен, кроме того, нам не особенно интересно гонять ядро на 12 МГц, когда оно отлично работает на 50 МГц.

Во-вторых, основную частоту можно задать еще с одного внутреннего генератора – watchdog oscillator, который обычно используется для работы watchdog. Этот осциллятор работает на скоростях (программно настраиваемо) от 9,4 кГц до 2,3 МГц с погрешностью ±40%, — казалось бы, не лучшее решение для основной частоты. С другой стороны – это именно то замечательное и энергоэффективное решение, если вам нужно перевести ядро в спящий режим, при этом оставив какую-то часть периферии рабочей.

В-третьих, мы можем получить основную частоту из системного осциллятора до или после ФАПЧ. Не будем сейчас вникать в специфику работы ФАПЧ, так как это достаточно объемная тема. Интересующимся советую изучить раздел «3.11 System PLL functional description».

⓶ Системный осциллятор

Системный осциллятор – это та часть процессора, которая не будет работать без аппаратных модификаций, в нем отсутствует основная рабочая сила осциллятора – кристалл (или кварцевый резонатор), который необходимо подключить снаружи, для чего на любом современном процессоре есть пины XTALIN/XTALOUT.

Конкретно LPC1114 (впрочем, как и остальные процессоры линейки LPC111x) поддерживает кристаллы с частотой осцилляции от 1 МГц до 25 МГц. Помимо самого кристалла, вам также понадобятся два конденсатора, значения которых зависят от параметров выбранного кристалла. Тут я отсылаю вас к datasheet, где в разделе 12.3 (XTAL input) есть и схема подключения, и таблица с рекомендованными емкостями конденсаторов. В тестовой схеме я пробовал использовать кристалл с частотой 12 МГц, емкостью нагрузки 20 пФ и двумя конденсаторами на 39 пФ, но этот режим работы далее рассматриваться не будет.

Если у вас есть надежный внешний источник тактовой частоты, то можно пропустить системный осциллятор, тогда тактовая частота берется с пина XTALIN.

Системный осциллятор можно использовать непосредственно как генератор основной частоты, или же предварительно пропустить его через ФАПЧ.

⓷ ФАПЧ

Не вдаваясь в электромеханику, ФАПЧ – это устройство, которое сначала умножает, а потом делит входную тактовую частоту. На входе ФАПЧ может принять частоту от IRC или системного осциллятора, а выход будет использован для основной частоты.

Настройка параметров ФАПЧ потенциально опасна для внутренностей процессора, потому я рекомендую NXP-шную утилиту (успешно конвертируется и работает в Google Drive) для подбора необходимых параметров, просто задайте частоту осциллятора на входе и итоговую частоту, которую хотите получить, и она рассчитает возможные варианты.

В сети есть интересная заметка о том, как поднять частоту IRC для генерации 50 МГц на выходе ФАПЧ, но для отладки этого результата вам понадобится осциллоскоп.

⓸ Системная частота

Обычно ядро (то, что Cortex-M0) работает на основной частоте, но, при необходимости, основную частоту можно разделить (на значение вплоть до 255), получив в итоге системную частоту. Помимо непосредственно ядра, на этой частоте будут работать флеш-память, RAM и вся периферия, за исключением SPI и UART. Имейте в виду, что максимальная частота тут – это 50 МГц.

⓹ А что же со SPI и UART?

Из-за специфики этих интерфейсов у них есть свои выделенные делители частоты, например, у UART он позволяет выбрать необходимый битрейт.

Несмотря на некоторую неочевидность схемы, на вход делителя попадает не основная, а системная частота.

Расчет делителя для битрейта – достаточно сложная задача, потому в очередной раз отправляю вас в инструкцию – «13.5.15 UART Fractional Divider Register (U0FDR — 0x4000 8028)». Там есть и формула расчета, и объяснение дополнительного дробного аргумента, а также блок-схема для поиска нужных параметров для заданного битрейта и пара примеров.

У SPI все как-то существенно проще, скорее всего потому, что мастер на шине задает частоту, и остальные устройства работают на ней – заочной синхронизации не требуется. Так что единственное, что мы можем сделать – это задать делитель. Важный момент – когда процессор работает в мастер-режиме, то минимальный делитель – 2, т.е., при частоте системной частоты в 48 МГц скорость передачи данных на SPI будет 24 МГц.

UPD: как верно заметил valeriyk, этот делитель не единственное, что влияет на выходную частоту. У SPI, например, несущая частота расчитывается по формуле: PCLK / (CPSDVSR * (SCR + 1)), где PCLK — это частота периферии; CPSDVSR — «предделитель»; SCR — количество тактов предделителя на один бит вывода.

⓺ Watchdog на страже жизнедеятельности

Watchdog по своей специфике — компонент изолированный. Поэтому, в качестве ведущей частоты можно использовать системную, IRC или отдельный осциллятор. Точно так же, у watchdog есть свой выделенный делитель.

Зачем для watchdog нужен отдельный тактовый генератор? Если программа случайно поломает основной генератор, конечно же! Тогда у нее все еще будет шанс быть перезагруженной по таймеру watchdog.

⓻ На выход

Наконец, процессор может генерировать выходной сигнал тактовой частоты на пине CLKOUT (одна из альтернативных функций у GPIO 0.1). В качестве ведущей частоты мы можем использовать любую из доступных нам: из осцилляторов (IRC, системного или watchdog) или системную частоту (после ФАПЧ, если он включен). Ну и, конечно, свой делитель.

Немного о mbed

Мы детально рассмотрели процесс генерации тактовой частоты в LPC1114, но что же с LPC1768? На самом деле, у каждой линейки процессоров может быть (и скорее всего будет свой особый подход, потому инструкцию по этой теме надо изучить предельно внимательно. В LPC1768 также есть внутренний осциллятор – IRC, но работает он на частоте 12 МГц. Помимо него есть основной (main) осциллятор, идентичный системному осциллятору. На mbed к нему подключен кристалл на 12 МГц. Наконец, есть осциллятор часов реального времени (RTC), но кристалл к нему не подключен.

Также, помимо основного ФАПЧ, есть дополнительный, который используется для генерации рабочей частоты USB. Все компоненты периферии имеют независимые настраиваемые делители относительно рабочей частоты.

Практические нюансы изменения частоты

Изменение рабочей тактовой частоты влечет за собой несколько последствий. Самое очевидное — необходимость перенастраивать таймеры. Также, потребуется переинициализация периферии, работающей с протоколами где важно зафиксировать несущую частоту (UART, USB). Наконец, количество тактов для доступа к флеш-памяти тоже играет важную роль. У LPC1114 значение по умолчанию — 3 такта (рабочая частота до 50 МГц, см. документацию по регистру FLASHCFG), чего вполне хватает для наших задач. Но у LPC1768 значение по умолчанию — 4 такта, с рабочей частотой до 80 МГц, чего нам будет недостаточно.

Тем не менее, работать на более высокой частоте, скорее всего, будет выгодно. Встраиваемые процессоры большую часть времени проводят в режиме сна, так что чем быстрее они отработают цикл бодрствования — тем меньше энергии они затратят в итоге.

За работу!

Теперь у нас есть необходимый теоретический багаж, и мы готовы применить полученные знания на практике – заставить светодиод мигать детерминировано, 1 раз в секунду.

Как вы видели раньше, очень много задач выполняются однотипно – записью и чтением регистров (вообще, все задачи выполняются именно так). ARM позаботилась о том, чтобы задачи, не привязанные к конкретному процессору, можно было выполнять одним и тем же кодом на C, для этого и существует CMSIS – набор драйверов для ядра процессора. Вендоры обычно расширяют его драйверами для всей остальной периферии.

Сложный момент с CMSIS состоит в том, что иногда не совсем понятно, где найти актуальную версию. Базовый набор файлов можно скачать непосредственно у ARM, на момент написания там доступна версия 3.01. Помимо заголовочных файлов, ARM предоставляет библиотеку для разноплановых сложных расчетов на DSP (которого в нашем железе все равно нет). Хуже обстоит дело с драйверами от конкретных производителей. У NXP, например, CMSIS для LPC1114 основан на CMSIS 1.30, а для LPC1768 – на 2.10. Более того, в наборе драйверов периферии есть явные ошибки в коде. А уж драйверы для чипов TI приходится основательно искать в гугле.

Из этого можно сделать два важных вывода: во-первых, код драйверов почти весь открыт, так что «доверяй, но проверяй»: инструкция и даташит — это ваша основная литература по работе с периферией. Во-вторых, в драйверах нет почти ничего, что нельзя было бы написать самому, т.е., это отличный и, зачастую, рабочий справочный материал. Главное – не забывать относиться к нему критически, если что-то выглядит странно – раскуривайте инструкцию по процессору.

Исходный код теперь несколько более структурирован. Хотя в результате он существенно вырос в количестве фалов, теперь намного проще поддерживать несколько разных платформ. Исходники для сегодняшнего примера доступны на GitHub: farcaller/arm-demos (pull-реквесты для новых архитектур приветствуются!).

Дерево исходников еще не до конца причесано, в частности, я не избавился от примитивных boot.s и memmap.ld. Следующая часть будет целиком посвящена вопросам компоновщика (включая сборку мусора и правильную инициализацию .data и .bss), где мы займемся добиванием до конца всех спорных моментов. Весь код разбит на три категории: в app/ находятся файлы «приложения» – непосредственно рабочий код примера. Он оформлен в стиле arduino, через функции setup() и loop(). В platform/ хранятся описания разных платформ и платформозависимые функции (кроме platform/common, файлы которого линкуются во все платформы). Наконец, в cpu/ находятся CMSIS для конкретных процессоров.

Весь этот комбайн собирается маленьким забавным Rakefile. Наверное, можно было бы обойтись и make, но хотелось все аккуратно собрать в одном файле, так что для сборки примеров вам пригодится руби не старше версии 1.9.

Работа по часам

Для реализации нашей задачи (напомню, нам надо мигать светодиодом ровно раз в секунду) нам пригодился бы какой-то таймер. К счастью, таймеров в LPC-шных процессорах сразу несколько, мы будем работать с самым унифицированным – SysTick. Этот таймер описан непосредственно в CMSIS, т.е., есть большая вероятность того, что он будет и в любом другом процессоре. Его предполагается использовать для измерения квантов времени при переключении задач в ОС, но ничего не мешает использовать его для простых задач.

SysTick – это простой таймер, который считает от заданного значения вниз до нуля, где он устанавливает бит переполнения, дергает прерывание и начинает считать сначала.

platform/common/systick.c:

void platform_systick_setup(unsigned int load)

{

SysTick->CTRL = 0x04;

SysTick->LOAD = load < 0xffffff ? load : 0xffffff;

SysTick->VAL = 0;

SysTick->CTRL = 0x05;

}

Для начала о синтаксисе. Эти замечательные структуры доступны нам из CMSIS, больше не надо запоминать, где находятся регистры, да и доступ к полям реализуется существенно нагляднее.

Для инициализации таймера мы записываем 4 в регистр контроля. Это выключает таймер, если он был включен, выключает прерывание и переводит SysTick на использование частоты процессора (напоминаю, что по умолчанию — это 12 МГц). Далее мы загружаем стартовую точку отсчета в регистр SYST_RVR, ограничивая максимум — 16777215, сбрасываем текущее значение регистра в ноль и запускаем таймер.

Теперь о том, как нам подождать одну секунду:

void platform_systick_wait()

{

volatile int i;

i = SysTick->CTRL;

while((i & 0x00010000) == 0) {

i = SysTick->CTRL;

}

}

Мы считываем значение COUNTFLAG из регистра SYST_CSR. COUNTFLAG выставляется в единицу, когда счетчик идет на новый круг, и сбрасывается в ноль при чтении. Таким образом, мы будем в цикле, пока счетчик не переполнится.

Заглянем в другие файлы нашего проекта. app/systick-blink.c:

#include "platform.h"

void setup()

{

platform_led_setup();

#if PLATFORM == MBED

platform_systick_setup(4000000);

#elif PLATFORM == PROTOBOARD

platform_systick_setup(12000000);

#else

#error Unknown platform

#endif

}

void loop()

{

platform_led_toggle(1);

platform_systick_wait();

platform_led_toggle(0);

platform_systick_wait();

}

Тут все достаточно наглядно. Инициализируем «драйвер» светодиода и таймера, и в цикле включаем-выключаем светодиод с задержкой. В зависимости от платформы, используем разное стартовое значение таймера (IRC на mbed и protoboard у нас работают на разных частотах). А как же работает код самого светодиода?

platform/protoboard/led.c:

#include "LPC11xx.h"

#define LED_PIN (1<<9)

void platform_led_setup()

{

LPC_GPIO1->DIR |= LED_PIN;

}

void platform_led_toggle(int on)

{

LPC_GPIO1->MASKED_ACCESS[LED_PIN] = on ? LED_PIN : 0;

}

Как видите, с CMSIS все стало действительно читабельнее. Единственный интересный момент — это то, что вместо общего регистра GPIO мы сейчас используем регистр с маской. Он позволяет устанавливать биты GPIO для конкретных пинов с маской, т.е., можно просто писать нужное значение, не думая о том, что надо сохранять состояние соседних пинов. Детальнее (и в картинках) об этом можно прочитать в инструкции: «12.4.1 Write/read data operation».

Для сравнения вот код для mbed. platform/mbed/led.c:

#include "LPC17xx.h"

#define LED_PIN (1<<18)

#define LED_PIN_IN_B2 (1<<2)

void platform_led_setup()

{

LPC_GPIO1->FIODIR |= LED_PIN;

}

void platform_led_toggle(int on)

{

LPC_GPIO1->FIOMASK2 |= ~LED_PIN_IN_B2;

if (on) {

LPC_GPIO1->FIOSET2 = LED_PIN_IN_B2;

} else {

LPC_GPIO1->FIOCLR2 = LED_PIN_IN_B2;

}

}

Как видите, он весьма схож. У LPC1768 нет возможности задавать маску прямо в адресе указателя, но зато есть побайтовый доступ к регистрам, что генерирует немного более эффективный ассемблерный листинг.

Собрать проект можно командой rake build_protoboard или rake build_mbed. Можно даже сразу прошить устройство: rake upload_protoboard TTY=/dev/ftdi/tty/device или rake upload_mbed MOUNT=/Volumes/MBED соответственно. Сейчас светодиоды мигают идентично на обоих устройствах.

Поиграем частотой?

Вроде бы мы и решили поставленную задачу — светодиод мигает с корректным интервалом, но что-то еще осталось за кадром. Максимальная рабочая частота LPC1114 — 50 МГц, а у LPC1768 и того больше — 100 МГц, получается, мы гоняем их едва ли в треть силы!

Настало время заняться правильной инициализацией платформы. platform/protoboard/init.c:

#define CLOCK_MODE_IRC 0 // 12 MHz

#define CLOCK_MODE_IRC_WITH_PLL 1 // 48 MHz

#define CLOCK_MODE_SYS_WITH_PLL 2 // 48 MHz with external 12MHz crystal

#define CLOCK_MODE CLOCK_MODE_IRC

В исходном коде доступны три шаблона для LPC1114: стандартные 12 МГц от IRC, 48 МГц от IRC, пропущенного через ФАПЧ, и 48 МГц от системного осциллятора, пропущенного через ФАПЧ. Последний вариант требует дополнительной аппаратной поддержки, но мы рассматриваем его, так как это очень актуальный режим использования.

void platform_init()

{

// set up system oscillator and toggle PLL to point at it

#if CLOCK_MODE == CLOCK_MODE_SYS_WITH_PLL

int i;

// power up system oscillator

LPC_SYSCON->PDRUNCFG &= ~(1 << 5);

// oscillator is not bypassed, runs at 1-20MHz range

LPC_SYSCON->SYSOSCCTRL = 0;

// allow circutry to settle down

for (i = 0; i < 200; ++i)

__NOP();

// set PLL clock source to system oscillator

LPC_SYSCON->SYSPLLCLKSEL = 1;

// wait for PLL clock source to be updated

LPC_SYSCON->SYSPLLCLKUEN = 1;

LPC_SYSCON->SYSPLLCLKUEN = 0;

LPC_SYSCON->SYSPLLCLKUEN = 1;

while (!(LPC_SYSCON->SYSPLLCLKUEN & 1))

;

#endif

Если мы работаем от системного осциллятора, его необходимо корректно инициализировать, а в первую очередь — включить. Как мы обсуждали ранее, осциллятор можно пропустить, если на входе XTALIN присутствует уже сформированный сигнал тактовой частоты.

После первичной инициализации следует сделать небольшую задержку. Далее мы переводим ФАПЧ на работу от системного осциллятора (вместо IRC), для этого существует интересный механизм: пишем 0, пишем 1, ждем — регистр начнет возвращать 1.

// set up PLL if it's used

#if CLOCK_MODE == CLOCK_MODE_IRC_WITH_PLL || CLOCK_MODE == CLOCK_MODE_SYS_WITH_PLL

// set up PLL dividers

LPC_SYSCON->SYSPLLCTRL = 0x23; // M = 3, P = 12MHz

// PLLout = 12MHz * (M+1) / P = 48MHz

// power up PLL

LPC_SYSCON->PDRUNCFG &= ~(1 << 7);

// wait until PLL is locked

while (!(LPC_SYSCON->SYSPLLSTAT & 1))

;

// switch main clock to be driven from PLL

LPC_SYSCON->MAINCLKSEL = 3;

// wait for main clock source to be updated

LPC_SYSCON->MAINCLKUEN = 1;

LPC_SYSCON->MAINCLKUEN = 0;

LPC_SYSCON->MAINCLKUEN = 1;

while (!(LPC_SYSCON->MAINCLKUEN & 1))

;

#endif

Вторая часть инициализирует ФАПЧ, который на данном этапе получает на входе сигнал или от IRC, или от системного осциллятора. Настраиваем делители по формуле из инструкции, включаем ФАПЧ и ждем, пока он заблокируется. Основная частота после загрузки работает от IRC, переводим ее на работу от выхода ФАПЧ и ждем, пока это изменение «устаканится».

На 48 МГц для SysTick нам понадобится 48000000 циклов, но это больше его максимального значения. Один из вариантов решения — ждать несколько циклов таймера, что реализовано в функции platform_systick_wait_loop (другим вариантом было бы использовать 32-разрядный таймер CT32B0).

У LPC1768 код, опять же, в целом похожий. Тут важный момент в том, что на выходе из PLL должно быть не менее 275 МГц, когда на входе в процессор — не более 100 МГц. В общем, внимательно проверяем делители. Также важно отметить, что мы повышаем количество тактов, необходимых для доступа к флеш-памяти, потому что мы будем работать на частоте выче чем значение по умолчанию.

platform/mbed/init.c:

// if we go for clock > 80 MHz, we need to set up flash access time

LPC_SC->FLASHCFG = (LPC_SC->FLASHCFG & 0xFFF) | 0x4000; // 4 cpu clocks

Код, приведенный в примере, актуален только для LPC1768 на mbed, так как привязан к конкретной частоте кристалла. Более того, если вы работаете с LPC1768 «напрямую», то его загрузчик стартует с IRC с включенным ФАПЧ, так что в своем инициализаторе его перед настройкой необходимо выключить.

Подводя итоги

Еще хотел сегодня рассказать про CLKOUT и о том, как можно контролировать частоту анализатором логики или осциллографом, но так статья получилась бы слишком большой. CLKOUT, 32-разрядные таймеры, прерывания и спящий режим — все это будет в следующих выпусках.

До меня доехала коробка со Stellaris LaunchPad, я подумаю над тем, как лучше всего будет добавить еще одну архитектуру, не раздувая повествование. В любом случае, LPC1114 становится основным целевым процессором, все примеры мы сначала будем обкатывать на нем.

Приношу свои извинения за «многобукаф», далее постараюсь писать более содержательно.

P.S. Как всегда, большое спасибо pfactum за вычитку текста и бесценные комментарии по электромеханике. И за то, что объяснил про ФАПЧ :-).

Это произведение доступно по лицензии Creative Commons «Attribution-NonCommercial-NoDerivs» 3.0 Unported. Программный текст примеров доступен по лицензии Unlicense (если иное явно не указано в заголовках файлов). Это произведение написано исключительно в образовательных целях и никаким образом не аффилировано с текущим или предыдущими работодателями автора.

Это произведение доступно по лицензии Creative Commons «Attribution-NonCommercial-NoDerivs» 3.0 Unported. Программный текст примеров доступен по лицензии Unlicense (если иное явно не указано в заголовках файлов). Это произведение написано исключительно в образовательных целях и никаким образом не аффилировано с текущим или предыдущими работодателями автора.

Только зарегистрированные пользователи могут участвовать в опросе. Войдите, пожалуйста.

О чем писать дальше?

48.88%

Прочитал, пищи еще!

196

6.98%

Прочитал, давай про компоновщик

28

2.99%

Прочитал, хочу детальнее про ассемблерный листинг на выходе

12

19.45%

Пролистал, если будет продолжение – тоже пролистаю

78

21.7%

Не читал, но голосовать люблю

87

Проголосовал 401 пользователь.

Воздержались 62 пользователя.

Демьян Бондарь

Эксперт по предмету «Электроника, электротехника, радиотехника»

преподавательский стаж — 5 лет

Задать вопрос автору статьи

Технологии цифровой связи

Определение 1

Цифровая связь – это область техники, которая связана с передачей цифровых данных.

Цифровая связь широко используется и для передачи аналоговых сигналов, для чего они дискретизируются. В цифровой связи используются следующие технологии:

- Кодирование источника информации.

- Шифрование данных.

- Сжатие данных.

- Помехоустойчивое кодирование.

- Модуляция.

- Помехоустойчивое кодирование.

Кодирование источника информации подразумевает решение задачи, которая связана с эффективным описанием исходной информации. Данный процесс допускает снижение требований по отношению к полосе частот или памяти, которые связаны с передачей и хранением дискретных реализаций исходных данных. Целью кодирования является получения описания исходной информации с допустимым уровнем точности при номинальной скорости передачи битов или допуск низкой скорости передачи, с целью получения описания источника с заданной точностью.

Для устранения помех в передаваемый сигнал вводится сконструированная избыточность, что способствует обнаружению и исправлению ошибок. Существует два основных класса помехоустойчивых кодов: сверточные и блочные. Сверточные коды работают с непрерывным потоком данных и кодируют их посредством сдвига с линейной обратной связи. Их декодирование может осуществляться при помощи алгоритма Витерби. Блочные коды преобразуют фиксированные блоки данных определенной длины в блоки другой длины. Декодирование каждого блока осуществляется отдельно и независимо от других. Примерами блочных кодов являются коды Рид – Соломона, коды Хемминга и другие.

Определение 2

Модуляция – это процесс преобразования одного или нескольких параметров высокочастотного несущего колебания по закону низкочастотного сообщения.

В результате модуляции спектр низкочастотного управляющего сигнала переносится в область высоких частот, что делает возможным настройку приемно-передающих устройств на разных частотах, чтобы они не “мешали” друг другу.

«Расчёт основных характеристик системы цифровой связи» 👇

Функциональные узлы системы цифровой связи. Порядок расчетов при проектировании системы цифровой связи

К основным функциональным узлам цифровой системы связи относятся:

- Источник сообщений.

- Кодер.

- Аналого-цифровой преобразователь.

- Формирователь модулирующих сигналов.

- Перемножители.

- Получатель сообщений.

- Фазовращатель.

- Цифро-аналоговый преобразователь.

- Генератор гармонических колебаний.

- Декодер.

- Сумматор.

- Преобразователь параллельного входа.

- Непрерывный канал.

- Демодулятор.

В состав расчетов при проектировании цифровой системы связи входят:

- расчет источника сообщений (плотность распределения мгновенных сообщений, построение графиков распределения сообщений и их плотности, дисперсия сообщений, спектральная плотность мощности, построение корреляционной функции),

- аналого-цифрового преобразователя (интервал дискретизации, число уровней квантования, мощность шума, число двоичных разрядов и т.п.),

- кодера (степень кодирования, векторы связи, последовательность кодовых символов, длина кодового ограничения),

- формирователя модулирующих сигналов, модулятора (построение графиков квадратурного, синфазного сигналов, а также кодовой последовательности),

- непрерывного канала (ширина частотной полосы, мощность помех, средняя мощность сигнала, пропускная способность, эффективность использования пропускной способности),

- демодулятора (построение схемы демодулятора, написание алгоритмов работы решающих устройств, оценка вероятности ошибки),

- декодера.

Пример расчета основных параметров цифровой системы связи

Исходными данными при расчете параметров цифровой системы связи являются верхняя частота и количество каналов цифровой связи. Для начала находится количество всех каналов, которые организовываются системой:

No = N + Nc

где, N – требуемое количество каналов цифровой связи; Nс – число каналов управления и синхронизации.

Период дискретизации или длительность цикла определяется по следующей формуле:

То = 1 / f0

где, f0 – частота дискретизации.

На практике частоту дискретизации подбирается таким образом, чтобы выполнялось следующее условие:

f0 = (2.3…2.4)Fв

где Fв – верхняя частота.

Рассчитав все предыдущие значения, теперь можно определить длительность канального интервала:

$Тк = То / NоТк = То / Nо

Отсюда, длительность тактового канала между кодовыми импульсами в канальном интервале рассчитывается следующим образом:

Тт = Тк / n

где, n – число разрядов в кодовой комбинации квантованного отсчета (определяется опытным путем или является исходным данным).

Длительность кодового импульса:

t = 0.5 • Тт

Формула для расчета тактовой частоты линейного сигнала выглядит следующим образом:

fт = No • n • fo

Длительность управляющих канальных импульсов:

tи = Тк / 3,5

Последней рассчитывается полоса пропускания линейного тракта:

D = 1 / t

Находи статьи и создавай свой список литературы по ГОСТу

Поиск по теме

Вычисляется тактовая частота процесора путем умножения частоты шины (ее еще называют базовой) на множитель. На примере процессора Intel i7 5600U с множителем 20 и базовой частотой шины 133МГц получаем частоту путем перемножения 133*20 итого 2,66 ГГц.

Как узнать частоту процессора Windows 10?

Для того, чтобы посмотреть текущую скорость работы процессора, запустим «Диспетчер задач» (Ctrl+Shift+Esc) и перейдем на вкладку «Производительность». Как видите, на данный момент нагрузка невелика и процессор работает вполсилы, частота его работы составляет 1.84ГГц.

Как узнать сколько ядер работает на Windows 10?

Определение количества ядер в процессоре

- Нажмите клавиши CTRL+SHIFT+ESC, чтобы открыть диспетчер задач.

- Выберите вкладку «Производительность», чтобы узнать, сколько ядер и логических процессоров есть на компьютере.

Что лучше тактовая частота или количество ядер?

Чем выше тактовая частота, тем больше операций может выполнить камень за единицу времени. Но этот показатель — не основной при определении производительности процессора. Стоит помнить, что порой важнее количество ядер/потоков, кэш-память частота шины процессора.

Какая самая большая частота процессора?

Сегодня компания AMD объявила о том, что процессор AMD FX был успешно разогнан до 8,429 ГГц. Эта частота является самой высокой частотой в мире, на которой когда-либо работал компьютерный процессор, что засвидетельствовали представители Книги рекордов Гиннесса.

Сколько ядер в процессоре лучше?

Количество ядер

Но лучше все же хотя бы 4 ядра — про запас. Для работы с графикой, 3D моделирования, игр и других действий, которые требуют серьезных вычислительных нагрузок, необходим вариант с 6-8 ядрами. Количество потоков тоже влияет на производительность.

Как вычисляется тактовая частота процессора?

Вычисляется тактовая частота процесора путем умножения частоты шины (ее еще называют базовой) на множитель. На примере процессора Intel i7 5600U с множителем 20 и базовой частотой шины 133МГц получаем частоту путем перемножения 133*20 итого 2,66 ГГц.

Чем больше тактовая частота тем лучше?

Чем больше (выше) тактовая частота, тем быстрее работает центральный процессор. Каждый микропроцессор имеет определенное число элементов памяти, называемых регистрами, арифметико-логическое устройство (АЛУ) и устройство управления.

Что такое тактовая частота информатика?

Тактовая частота — частота синхронизирующих импульсов синхронной электронной схемы, то есть количество синхронизирующих тактов, поступающих извне на вход схемы за одну секунду. Обычно термин употребляется применительно к компонентам компьютерных систем.

Это произведение доступно по лицензии Creative Commons «Attribution-NonCommercial-NoDerivs» 3.0 Unported. Программный текст примеров доступен по лицензии Unlicense (если иное явно не указано в заголовках файлов). Это произведение написано исключительно в образовательных целях и никаким образом не аффилировано с текущим или предыдущими работодателями автора.

Это произведение доступно по лицензии Creative Commons «Attribution-NonCommercial-NoDerivs» 3.0 Unported. Программный текст примеров доступен по лицензии Unlicense (если иное явно не указано в заголовках файлов). Это произведение написано исключительно в образовательных целях и никаким образом не аффилировано с текущим или предыдущими работодателями автора.