Содержание

- Самостоятельное изучение схемотехники. Основные понятия. Часть 1

- Проектирование логических схем с помощью функций алгебры логики

- Разработка электрической схемы цифрового устройства

- Описание разрабатываемого цифрового блока. Общие сведения и электрическая схема стандартных базовых дигитальных элементов. Особенность вычислений элементарного арифметического действия с помощью устройства. Основная характеристика диаграмм сигналов.

- Отправить свою хорошую работу в базу знаний просто. Используйте форму, расположенную ниже

- 2. Описание разрабатываемого цифрового блока

- 3. Общие сведения и электрическая схема стандартных базовых цифровых элементов

- 4. Функциональное назначение разрабатываемого блока

- 5. Описание функциональной схемы

- 6. Описание электрической схемы

- Заключение

- Библиографический список

- В качестве прототипа разрабатываемого устройства возьмем микросхему К556РТ1. Она представляет собой 2 матрицы: элементов «И» (с инверторами) и элементов «искл. ИЛИ» (структура ДНФ). Кроме того, в составе микросхемы (см. Рис. 2) находятся адресные формирователи FA1 и FA2, а также программируемый дешифратор DC PR, необходимые для программирования устройств. К556РТ1 имеет 16 входов A0 — A15 и 8 выходов D0 — D7. Каждая функция, которую вычисляет ПЛМ, может содержать до 48 конъюнкций.

- Рисунок 2. Структурная схема К556РТ1

- Для того чтобы микросхема могла выполнять определенные функции (например делитель целых чисел) её необходимо запрограммировать (у ИМС имеется специальный вход для подтверждения записи), причем запрограммировать ПЛМ можно всего лишь 1 раз, так как при записи происходит уничтожение (пережигание) проводников внутри кристалла микросхемы. Перед программированием ПЛМ требуемые функции необходимо оптимизировать, с целью более эффективного использования микросхемы (учитывая, что потребляемый ток не зависит от количества используемых элементов). Так, например, с помощью К556РТ1 можно бы было выполнить делитель, с большей разрядностью, чем у проектируемого устройства (в зависимости от степени оптимизации). Использование элементов «искл. ИЛИ» во втором уровне данного ПЛМ позволяет с помощью логического уровня на входе 2 ножки микросхемы получать прямые или инверсные выходные значения.

- Рисунок 3. Функциональная схема К556РТ1

- После выходов элементов «искл. ИЛИ» в ПЛМ установлены вентили на элементах «И», необходимые для разрешения или блокирования выполнения операций (вход OE).

- Рисунок 4. Обозначение ПЛМ на принципиальной схеме

- 2. Описание разрабатываемого цифрового блока

- 4. Функциональное назначение разрабатываемого блока

- 5. Описание функциональной схемы

- Функциональная схема цифрового блока аналогична структурной схеме (см. Рис. 1). Устройство ПЛМ (по ДНФ) включает в себя два уровня:

- Подобные документы

Самостоятельное изучение схемотехники. Основные понятия. Часть 1

Изучение цифровой схемотехники нужно начинать с теории автоматов. В этой статье можно найти некоторые элементарные вещи, которые помогут не потеряться в дальнейших статьях. Я постарался сделать статью легкочитабельной и уверен, что неподготовленный читатель сможет в ней легко разобраться.

Сигнал — материальный носитель информации, используемый для передачи сообщений по системе связи. Сигнал, в отличие от сообщения, может генерироваться, но его приём не обязателен (сообщение должно быть принято принимающей стороной, иначе оно не является сообщением, а всего лишь сигналом).

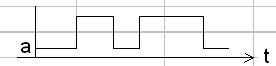

В статье рассматривается цифровой дискретный сигнал. Это такой сигнал, который имеет несколько уровней. Очевидно, что двоичный сигнал имеет два уровня — и их принимают за 0 и 1. Когда высокий уровень обозначается единицей, а низкий нулем — такая логика называется позитивной, иначе негативной.

Цифровой сигнал можно представить в виде временной диаграммы.

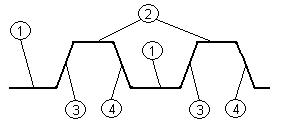

В природе дискретных сигналов не существует, по этому их заменяют аналоговыми. Аналоговый сигнал не может перейти из 0 в 1 мгновенно, по этому такой сигнал обладает фронтом и срезом.

Если рисовать упрощенно то это выглядит так:

1 — низкий уровень сигнала, 2 — высокий уровень сигнала, 3 — нарастание сигнала (фронт), 4 — спад сигнала (срез)

Сигналы можно преобразовывать. Для этого на практике используются логические элементы, а чтобы это записать формально используются логические функции. Вот основные:

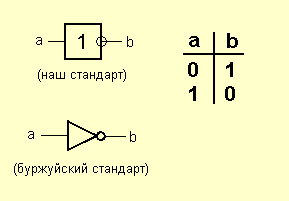

Отрицание — инвертирует сигнал.

На схемах обозначается так:

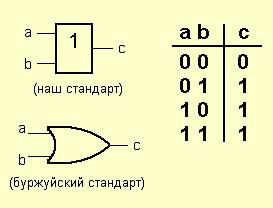

Логическое ИЛИ (логическое сложение, дизъюнкция)

На схеме:

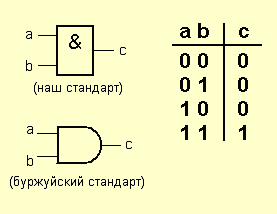

Логическое И (логическое умножение, конъюнкция)

На схеме:

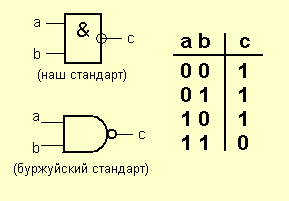

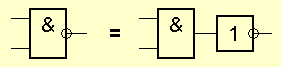

Последние два могут иметь отрицание на выходе (И-НЕ, ИЛИ-НЕ). Значения их логических функций инвертируются, а на схеме выход рисуется кружочком.

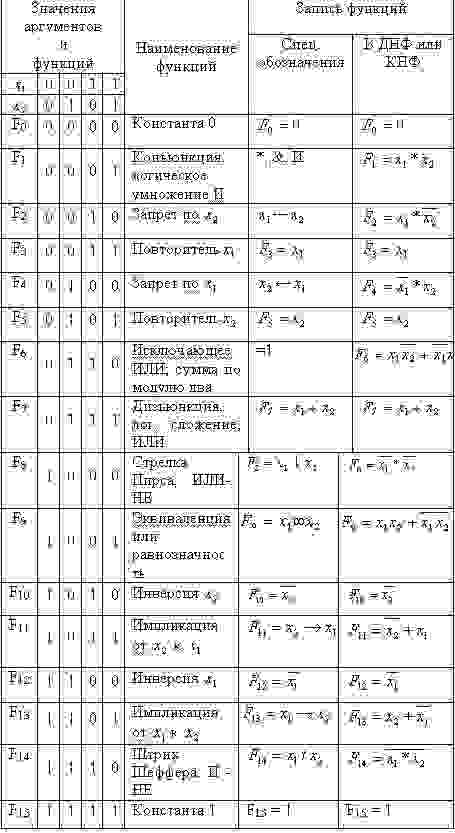

Сводная таблица логических функций двух аргументов выглядит так:

Работа с логическими функциями основывается на законах алгебры логики, основы которых изложены в прикрепленном файле. Так же там есть задания для самоконтроля и контрольные вопросы по теме.

Проектирование логических схем с помощью функций алгебры логики

Логической схемой называется совокупность логических электронных элементов, соединенных между собой таким образом, чтобы выполнялся заданный закон функционирования схемы, иначе говоря, — выполнялась заданная логическая функция.

По зависимости выходного сигнала от входного все электронные логические схемы можно условно разбить на:

Схемы первого рода, т.е. комбинационные схемы, выходной сигнал которых зависит только от состояния входных сигналов в каждый момент времени;

Схемы второго рода или накапливающие схемы (схемы последовательностные), содержащие накапливающие схемы (элементы с памятью), выходной сигнал которых зависит как от входных сигналов, так и от состояния схемы в предыдущие моменты времени.

По количеству входов и выходов схемы бывают: с одним входом и одним выходом, с несколькими входами и одним выходом, с одним входом и несколькими выходами, с несколькими входами и выходами.

По способу осуществления синхронизации схемы бывают с внешней синхронизацией (синхронные автоматы), с внутренней синхронизацией (асинхронные автоматы являются их частным случаем).

Практически любой компьютер состоит из комбинации схем первого и второго рода разной сложности. Таким образом, основой любого цифрового автомата, обрабатывающего цифровую информацию, являются электронные элементы двух типов: логические или комбинационные и запоминающие. Логические элементы выполняют простейшие логические операции над цифровой информацией, а запоминающие служат для ее хранения. Как известно, логическая операция состоит в преобразовании по определенным правилам входной цифровой информации в выходную.

Можно считать, что элементарные логические функции являются логическими операторами упомянутых электронных элементов, т.е. схем. Каждая такая схема обозначается определенным графическим символом. (Они были представлены выше — Элементы И, ИЛИ, НЕ, ИЛИ-НЕ, И-НЕ)

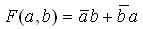

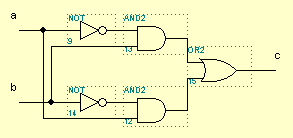

В качестве примера ниже представлена схема электрическая функциональная логического преобразователя (комбинационного автомата), реализующего логическую функцию  в элементном базисе из логических элементов И, ИЛИ, НЕ.

в элементном базисе из логических элементов И, ИЛИ, НЕ.

Для закрепления предлагаю, самостоятельно синтезировать логическую схему, реализующую следующие логические функции:

Сделать это можно к примеру в Electronic workbench.

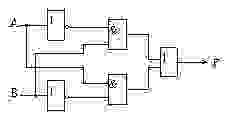

Вот для примера первое выполненное задание:

Hint: Для того чтобы включить условные обозначения в соответствии с отечественными ГОСТ-ами в файл настроек EWB.INI нужно добавить строку DIN = ON

На этом первая часть статьи заканчивается. Надеюсь, что она была не слишком утомительной. Все вышеописанное необходимо для понимания принципов работы с сигналами в электрических схемах. В следующей статье будут рассмотрены способы минимизации логических функций, понятие абстрактного автомата и пример синтеза RS-триггера.

Источник

Разработка электрической схемы цифрового устройства

Описание разрабатываемого цифрового блока. Общие сведения и электрическая схема стандартных базовых дигитальных элементов. Особенность вычислений элементарного арифметического действия с помощью устройства. Основная характеристика диаграмм сигналов.

Отправить свою хорошую работу в базу знаний просто. Используйте форму, расположенную ниже

Студенты, аспиранты, молодые ученые, использующие базу знаний в своей учебе и работе, будут вам очень благодарны.

Размещено на http://www.allbest.ru/

Министерство образования и науки РФ

Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования

«Тульский государственный университет»

Кафедра «Робототехника и автоматизация производства»

по дисциплине «Микропроцессоры, цифровые устройства и схемотехника БМиП»

Разработать и протестировать (в программе Electronics Workbench) электрическую схему цифрового устройства, реализованную на элементах «И», « ИЛИ», «НЕ» и RS-DC триггерах. В соответствие с вариантом задания, устройство должно быть построено на базе программируемой логической матрицы и должно выполнять функцию деления. Вход делимого должен быть четырехразрядным, вход делителя трехразрядным, выход частного должен быть четырехразрядным.

1. Общие сведения и электронная схема прототипа

2. Описание разрабатываемого цифрового блока

3. Общие сведения и электрическая схема стандартных базовых цифровых элементов

4. Функциональное назначение разрабатываемого блока

5. Описание функциональной схемы

6. Описание электрической схемы

Заключение

Библиографический список

В качестве прототипа разрабатываемого устройства возьмем микросхему К556РТ1. Она представляет собой 2 матрицы: элементов «И» (с инверторами) и элементов «искл. ИЛИ» (структура ДНФ). Кроме того, в составе микросхемы (см. Рис. 2) находятся адресные формирователи FA1 и FA2, а также программируемый дешифратор DC PR, необходимые для программирования устройств. К556РТ1 имеет 16 входов A0 — A15 и 8 выходов D0 — D7. Каждая функция, которую вычисляет ПЛМ, может содержать до 48 конъюнкций.

Рисунок 2. Структурная схема К556РТ1

Для того чтобы микросхема могла выполнять определенные функции (например делитель целых чисел) её необходимо запрограммировать (у ИМС имеется специальный вход для подтверждения записи), причем запрограммировать ПЛМ можно всего лишь 1 раз, так как при записи происходит уничтожение (пережигание) проводников внутри кристалла микросхемы. Перед программированием ПЛМ требуемые функции необходимо оптимизировать, с целью более эффективного использования микросхемы (учитывая, что потребляемый ток не зависит от количества используемых элементов). Так, например, с помощью К556РТ1 можно бы было выполнить делитель, с большей разрядностью, чем у проектируемого устройства (в зависимости от степени оптимизации). Использование элементов «искл. ИЛИ» во втором уровне данного ПЛМ позволяет с помощью логического уровня на входе 2 ножки микросхемы получать прямые или инверсные выходные значения.

Рисунок 3. Функциональная схема К556РТ1

После выходов элементов «искл. ИЛИ» в ПЛМ установлены вентили на элементах «И», необходимые для разрешения или блокирования выполнения операций (вход OE).

Рисунок 4. Обозначение ПЛМ на принципиальной схеме

2. Описание разрабатываемого цифрового блока

Постановка задачи и анализ возможных вариантов ее функционирования.

Целью контрольно-курсовой работы является овладение студентами основными навыками анализа и применения основных дискретных элементов цифровой комбинационной схемотехники при создании устройств, решающих задачу преобразования информации различного назначения и применяемых в микропроцессорных системах с вычислителями.

Задачей работы является разработка функциональной и электрической принципиальной схем устройства и проведения тестовых испытаний при помощи моделирования.

В данной работе требуется разработать делитель на базе программируемой логической матрицы (ПЛМ). Устройство будет состоять условно из двух частей. Первая часть будет определять различные комбинации на входе ПЛМ, а вторая часть суммировать комбинации (для каждого разряда), при которых на данном разряде появляется одинаковый результат.

Следует отметить, что выбор построения устройства на базе ПЛМ обусловливается относительной простотой построения схемы (при небольших количествах разрядов), высоким быстродействием (по сравнению устройств на базе сумматора). Однако имеются и недостатки данного метода: высокое энергопотребление из-за большого количества элементов (микросхем); большая конструкция, усложняющая реализацию. Частично энергопотребление (и конструкцию) можно уменьшить, используя упрощения при проектировании, в частности правило поглощения (из дискретной математики). Таким образом, можно значительно упростить схему проектируемого устройства.

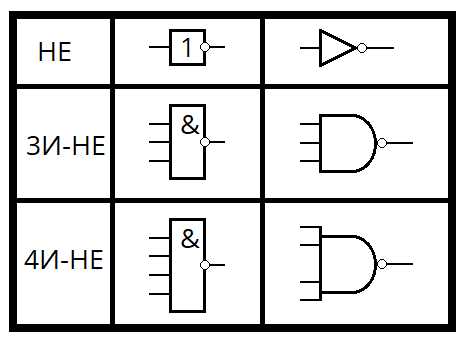

3. Общие сведения и электрическая схема стандартных базовых цифровых элементов

Программируемая логическая матрица представляет собой схему, состоящую из 2-ух уровней. Логические элементы, на которых выполнены данные уровни, выбираются на основании выбранного при проектировании математического аппарата (ДНФ, КНФ), семейства микросхем (ТТЛ, КМОП и т. д.), а также методов оптимизации устройства. Построение ПЛМ производится с помощью таблицы истинности, в которой должны быть запрограммированы функции устройства. При этом, простейшие булевы функции, вычисленные из таблицы, могут приводиться как к ДНФ (дизъюнктивной нормальной форме), так и к КНФ (конъюнктивной нормальной форме), что впоследствии и определяет базу элементов, на которых выполняются уровни ПЛМ. В контрольно-курсовой работе функции будут приводиться к ДНФ (более распространенной в ТТЛ логике). Ниже приведена структурная схема ПЛМ, построенная на основе функций в ДНФ.

Рисунок 1. Структурная схема ПЛМ.

4. Функциональное назначение разрабатываемого блока

5. Описание функциональной схемы

Функциональная схема цифрового блока аналогична структурной схеме (см. Рис. 1). Устройство ПЛМ (по ДНФ) включает в себя два уровня:

1) на первом уровне расположены элементы «И» с инверторами, служащие для определения своих (уникальных) комбинаций на входах ПЛМ;

2) на втором уровне расположены элементы «ИЛИ», которые объединяют комбинации, при которых значения на выходных разрядах будет одинаковым (равные Лог. 1).

В общем случае количество элементов «И» должно быть равно количеству комбинаций на входах (на входах делимого 4 разряда, т. е. 16 комбинаций, на входе делителя 3 разряда, т. е. 8 комбинаций, всего 128 комбинаций). Количество инверторов должно быть равно общему количеству входных разрядов, в нашем случае 7. А количество элементов «ИЛИ» равно количеству выходов, т. е. 4.

В результате такой организации в блоке будет использоваться большое количество микросхем, что может вызвать трудности при исполнении устройства. Для исключения последнего, схема оптимизируется, за счет простейших свойств булевой алгебры (исключением элементов, определяющих операции с одинаковым результатом).

6. Описание электрической схемы

Электрическая схема блока вынесена в Приложение 1.

Электрическая схема выполнена на основе элементов ТТЛ: «И» и «ИЛИ». Схема арифметического делителя на ПЛМ строится на базе булевых функций (приведенных к ДНФ), определенных из таблицы истинности устройства, в которой и определены функции работы блока. Перед созданием устройства функции оптимизируются.

Далее представлена таблица истинности делителя на базе ПЛМ.

По составленной таблице истинности определяем значение функций разрядов выхода устройства, с помощью простейших булевых операций (приводим к ДНФ), а кроме того упрощаем функции по правилу склеивания (правило склеивания для ДНФ ). Из-за большого количества комбинаций упрощение функций производим в программе «CarnoMinimizer».

Таким образом, в электрической схеме устройства ПЛМ на двух уровнях будут расположены элементы «И» и «ИЛИ». На первом уровне входы элементов присоединяются к соответствующим операндам в скобках (1 элемент выполняет действия с операндами одной скобки), причем общее количество таких элементов равно количеству скобок, т. е. 14. Входы элементов второго уровня, подключаются к выходам элементов первого уровня, причем количество подключений определяется количеством скобок для каждой функции, а общее количество элементов равно количествам выходов устройства, т. е. 4.

Тестовая электрическая схема вынесена в Приложение 2.

Для того чтобы протестировать разработанную схему к ее входам надо подключить входы X (делимое), Y (делитель), а к выходу датчики. Для генерации всех комбинаций используем генератор G (частотой 4000 Гц и скважностью 50%), который подключен 7 разрядный счетчик (128 комбинации). С четырех младших разрядов снимается сигнал делимого, а с трех старших сигнал делителя. Так как счетчики выполнены на базе DC триггеров, то инверторы из схемы устройства убираются, а инверсные сигналы снимаются непосредственно с выходов DC триггеров.

К генератору (для проверки правильности работы счетчиков), к прямым выходам счетчика, а также выходам разработанного блока подключаются входы цифрового анализатора, с которого снимаются диаграммы работы схемы.

Описание диаграмм сигналов.

Диаграммы сигналов вынесены в Приложение 3.

На диаграмме выведены следующие сигналы:

G — сигнал с задающего генератора (4000 Гц 50%);

— сигналы на входных разрядах — делимое;

— сигналы на входных разрядах — делитель;

— сигналы на выходных разрядах — частное;

Ширина исследуемого участка диаграммы должна быть не менее 128 комбинаций на входе (или 128 импульсов задающего генератора), с целью проверки правильности работы блока при всех комбинациях, закодированных в таблице истинности. Для наглядности это значение увеличивается (берется с запасом), чтобы убедиться, что устройство в другой момент времени работает аналогично, то есть является простой комбинационной схемой. Рассмотрение диаграммы при ширине, значительно превышающих 128 импульсов задающего генератора, бессмысленно, так как это уменьшает наглядность (уменьшается масштаб), а каждые 128 импульсов комбинации на выходе будут повторяться.

В ходе выполнения данной контрольно-курсовой работы были получены и применены на практике навыки конструирования цифровых устройств на элементах булевой логики. Было разработано устройство арифметического делителя. Полученные диаграммы сигналов показывают, что устройство правильно выполняет поставленные задачи, в соответствие с запрограммированными в таблице истинности функциями.

1. Шило В.Л. Популярные цифровые микросхемы: Справочник. 2-е изд., испр. — Челябинск: Металлургия, Челябинское отд., 1989. — 352с.: ил. — (Массовая радиобиблиотека. Вып.111).

2. Токарев В.Л. Аппаратные средства вычислительной техники : учеб. пособие для вузов / В.Л.Токарев .— Тула : Изд-во ТулГУ, 2005 .— 470c. — (75-летию ТулГУ посвящается) .— Библиогр.в конце кн. — ISBN 5-7679-0762-5 /в пер./ : 230.00.

Подобные документы

Описание функциональной схемы цифрового устройства для реализации микроопераций. Выбор элементной базы для построения принципиальной электрической схемы цифрового устройства. Разработка и описание алгоритма умножения, сложения, логической операции.

курсовая работа [684,0 K], добавлен 28.05.2013

Разработка электрической схемы цифрового устройства на основе базовых интегральных микросхем: упрощение и преобразование; выбор типа логики и конкретных серий. Электрический расчет цифровой схемы, расчет мощностей. Создание топологии в гибридном варианте.

курсовая работа [610,3 K], добавлен 29.09.2014

Разработка топологии базисных элементов и цифрового комбинационного устройства в целом в программе Microwind. Моделирование базисных логических элементов и функциональная схема демультиплексора. Схемотехническое проектирование цифрового устройства.

курсовая работа [1,7 M], добавлен 27.02.2012

Проектирование устройства преобразования цифровой информации в аналоговую и наоборот для цифрового магнитофона. Описание используемых интегральных микросхем. Разработка структурной и принципиальной схемы цифрового канала звукозаписи без кодера и декодера.

курсовая работа [1,8 M], добавлен 18.10.2010

Разработка общего алгоритма и функционирования цифрового фильтра. Составление и описание электрической принципиальной схемы устройства, расчет его быстродействия. Листинг программного модуля вычисления выходного отсчета. Оценка устойчивости устройства.

курсовая работа [236,2 K], добавлен 03.12.2010

Источник

При разработке

цифрового прибора используются модели

представления цифровых схем: логическая

модель, модель с временными задержками,

модель с учетом электрических эффектов

(или электрическая модель).

Первая модель

применима для всех цифровых схем,

работающих с низкой скоростью, в которых

быстродействие не принципиально.

Вторая модель

учитывает задержки срабатывания

логических элементов. Ее применение

необходимо для всех быстродействующих

устройств и для случая одновременного

изменения нескольких входных сигналов.

Третья модель

учитывает входные и выходные токи,

входные и выходные сопротивления и

емкости элементов. Эту модель надо

применять при объединении нескольких

входов и выходов, при передаче сигналов

на большие расстояния и при нетрадиционном

включении логических элементов (с

переводом их в аналоговый или в линейный

режимы).

На рисунке 1.14 на

примере простейшего логического элемента

инвертора показаны три модели представления

этого цифрового «прибора».

Рис. 1.14 – Три модели

представления цифрового устройства

Из рисунка видно,

что в первой, логической модели (1),

считается, что элемент срабатывает

мгновенно, любое изменение уровня

входного сигнала сразу же, без всякой

задержки приводит к изменению уровня

выходного сигнала.

Во второй модели

(2) выходной сигнал изменяется с некоторой

задержкой относительно входного.

В третьей модели

(3) выходной сигнал не только задерживается

по сравнению с входным, но и его изменение

происходит не мгновенно – процесс смены

уровней сигнала (фронт

сигнала) имеет

конечную длительность. Кроме того,

третья модель учитывает изменение

уровней логических сигналов.

В начале проектирования

используется первая модель, а затем для

некоторых узлов применяется вторая или

(реже) и третья модель.

При этом первая

модель не требует вообще никаких цифровых

расчетов, для нее достаточно только

знание таблиц истинности или алгоритмов

функционирования микросхем.

Вторая модель

предполагает расчет временных задержек

элементов на пути прохождения сигналов,

рисунок

1.15. В результате этого расчета может

выясниться, что требуется внесение

изменений в схему.

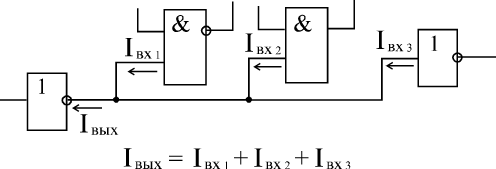

Рис. 1.15 – Суммирование

задержек элементов

Расчеты по третьей

модели могут быть различными, в том

числе и довольно сложными, но в большинстве

случаев они все-таки сводятся всего

лишь к суммированию входных и выходных

токов логических элементов, рисунок

1.16.

Рис. 1.16 – Суммирование

входных токов элементов

В результате этих

расчетов может выясниться, что требуется

применение микросхем с более мощными

выходами или включение дополнительных

элементов.

1.6. Общие требования к оформлению схем

Все электрические

схемы, выполняемые в рамках лабораторной

работы, должны изображаться согласно

требованиям ЕСКД: ГОСТ 2.702-75, 2.743-82,

2.708-81, 2.701-84 и т.д. Схемы электрические

принципиальные являются основным

чертежом лабораторных работ.

Принципиальная

схема определяет полный состав элементов

и связей между ними. Все интегральные

микросхемы и электронные компоненты

на ней изображаются в виде их

условно-графического обозначения (УГО),

рисунок 1.17.

Рис. 1.17 –

Условно-графическое обозначение и

размеры ЛЭ с двумя входами

При этом обязательно

указывается нумерация выводов интегральной

микросхемы. Выводы «Питание» и «Общий»

могут не изображаться. Корпуса интегральных

микросхем на чертежах должны иметь

позиционное обозначение. Рекомендуется

использовать следующее позиционное

обозначение: DDN (N – номер очередного

корпуса). Позиционное обозначение

выполняется сверху вниз, слева направо.

Для наглядного изображения схемы на

чертеже корпус интегральной микросхемы

может изображаться в конкретном месте

по отдельным элементам. В этом случае

при позиционном обозначении указывается

также номер элемента в корпусе, например,

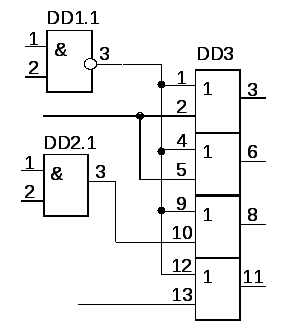

DD2.1 (2-й корпус, 1-й элемент), рисунок 1.18.

Рис. 1.18 – Фрагмент

схемы

При возможности

линии связи объединяются в шины, рисунок

1.19. Линия связи, которая входит в шину,

должна иметь уникальный в пределах шины

числовой номер или уникальное

буквенно-цифровое обозначение. Отводы

линий от шины рекомендуется выполнять

под прямым углом. Шину на чертеже

рекомендуется выполнять толщиной 2-3

мм. Толщина линий связи – не более 1 мм.

Обозначение сигнала, входящего

(выходящего) в (из) шины рекомендуется

производить у самой шины. Обозначение

сигналов, входящих в шину, должно

однозначно соответствовать сигналам,

выходящим из шины. Расстояние между

линиями сигналов – не менее 0,5 см.

На рисунке 1.20

показаны рекомендуемые размеры при

изображении ЛЭ, линий связи и шин на

принципиальной схеме. Все ответвления

от линий связи на чертеже изображаются

точками.

|

|

|

|

Рис. 1.19 |

Рис. 1.20 – |

Пример проектирования цифрового устройства «на пальцах»

Время на прочтение

3 мин

Количество просмотров 23K

Привет, Хабр! Это начало небольшого цикла из двух статей с пошаговым проектированием цифрового устройства с уклоном на практику. Минимум «воды» и максимум практики!

Для начала работы возьмем следующие выходные параметры: 0000110001110001

Примечание: существует множество способов и программ для проектирования цифровых устройств. Показанное в статье может отличаться от привычных вам. Это нормально.

Инструменты, материалы и прочее:

- Electronics Workbench

- Линейка, ручка и листок (для общих расчетов)

- Базовые знания дискретной математики, цифровой схемотехники и принципа работы представленных программ

- Условное графическое обозначение микросхем 7404 (аналог К155ЛН1), 7410 (аналог К155ЛА4), 7410 (аналог К155ЛА4) и 7420 (аналог К155ЛА1)

- Фактическое изображение микросхем 7404 (аналог К155ЛН1), 7410 (аналог К155ЛА4), 7410 (аналог К155ЛА4) и 7420 (аналог К155ЛА1)

Начало работы

1. Построение таблицы истинности и нахождение совершенной дизъюнктивной нормальной формы (СДНФ)

Первым делом необходимо составить таблицу истинности по формуле

где N – количество возможных вариантов, а i – количество выходных сигналов.

В представленном случае это будет выглядеть так:

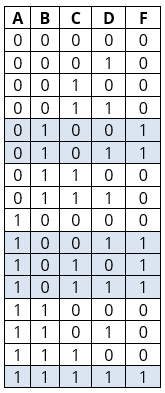

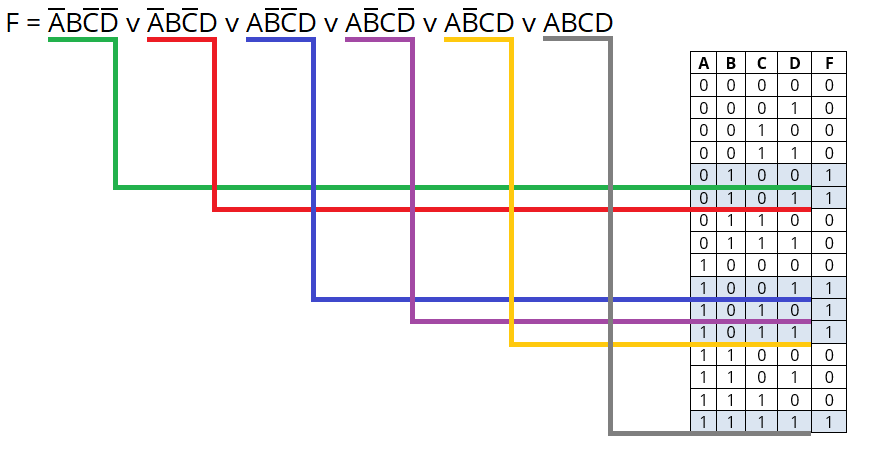

На основе полученных данных можно перейти к построению таблицы истинности. Для наглядности входные сигналы были обозначены как A, B, C и D, выходной как F.

После построения таблицы истинности можно приступать к получению СДНФ. Это выполняется в два шага:

- Выделяются строчки таблицы истинности, в которых F=1.

- Выписывается конъюнкция переменных у всех выделенных строк по следующей формуле: если значение переменной равно 1, то в конъюнкцию включается сама переменная. Если значение равно 0, то включается отрицание переменной. Полученные конъюнкции нужно связать в дизъюнкцию.

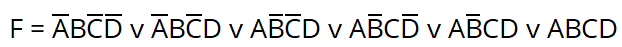

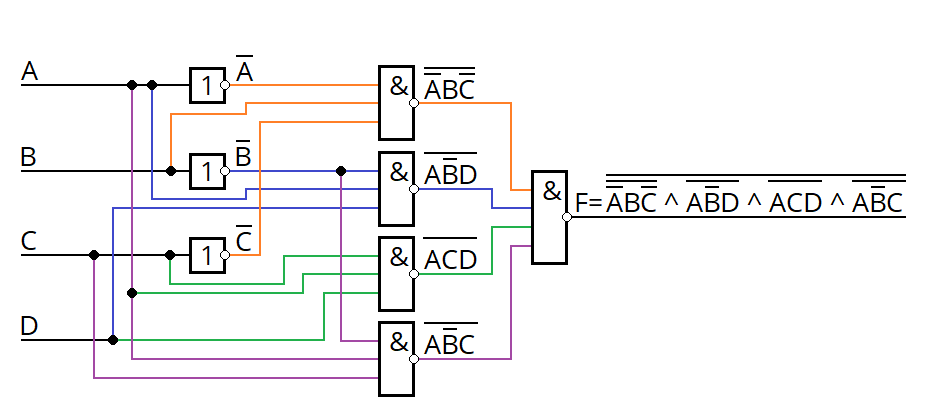

По итогу выходит такая СДНФ:

Более наглядно:

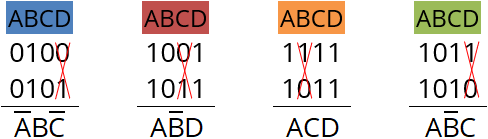

2. Создание карты Карно, минимизация и приведение к базису И-НЕ

Полученную СДНФ необходимо сократить при помощи карт Карно.

Три шага для построения карт Карно:

- так как используются четыре переменные (A, B, C и D), то строится таблица 5×5 клеток;

- таблица заполняется на основе «координат» из таблицы истинности (из строк, в которых F=1) или СДНФ (суть одна. Просто кому как удобнее);

- в заключение смежные клетки объединяются в группы. Группы не должны содержать нули. Группы должны быть кратны двум. Группы могут пересекаться.

В итоге получилось 4 группы:

Более наглядно:

Следующее действие — минимизация полученных групп. Общий принцип можно свести к следующему:

Если 11 — значение не меняется;

Если 00 — присваивается отрицание;

Если 01 (или 10) — вычеркивается.

Полученные произведения связываются в дизъюнкцию:

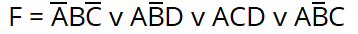

После чего составленное выражение приводится к базису И-НЕ при помощи закона де Моргана (отрицание конъюнкции есть дизъюнкция отрицаний, отрицание дизъюнкции есть конъюнкция отрицаний):

Обратите внимание на изменения — появилось двойное отрицание (по одной на «группу» и одно общее) и изменились знаки.

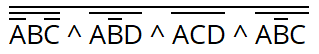

По желанию также можно составить логическую схему. Почему по желанию? Потому что дальше будет составление электронной схемы на основе логических элементов, а она, по своей сути, является той же самой логической схемой, но с возможностью проверки работоспособности.

Пример логической схемы:

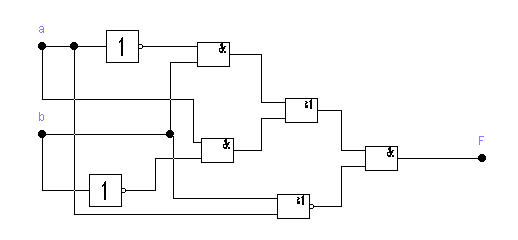

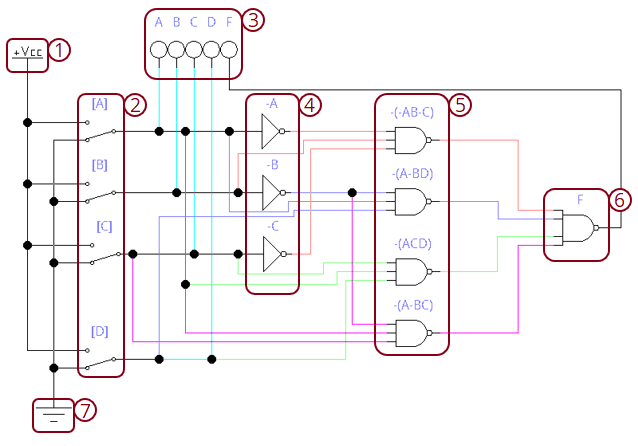

3. Электронная схема на основе логических элементов

Основные расчеты завершены. Теперь можно отложить листок с ручкой и линейкой. Переходим в Electronics Workbench.

В данном случае этот этап выступает «промежуточным» и упрощает процесс перехода от выражения в базисе И-НЕ к электронной схеме на основе микросхем.

Более наглядно:

1 — Питание;

2 — Переключатели, используемые для подачи сигналов;

3 — Индикаторы (применяются для наглядной проверки работоспособности);

4 — Логические элементы типа «НЕ»;

5 — Логические элементы типа «3И-НЕ»;

6 — Логический элемент типа «4И-НЕ»;

7 — Заземление.

Как можно заметить, логические элементы электронной схемы внешне отличаются от тех, что были представлены ранее (в логической схеме). Это связано с тем, что в Electronics Workbench условное графическое обозначение логических элементов выполнено по стандартам ANSI, тогда как показанная ранее логическая схема была выполнена в соответствии ГОСТ 2.743-91.

Идем дальше.

Работоспособность электронной схемы проверяется по таблице истинности. Для этого нужно нажать кнопку запуска

и начать производить переключения, проводя сравнение с таблицей истинности.

Пример:

ВАЖНО: нужно проверять каждую строчку. Выборочная проверка ничего не даст.

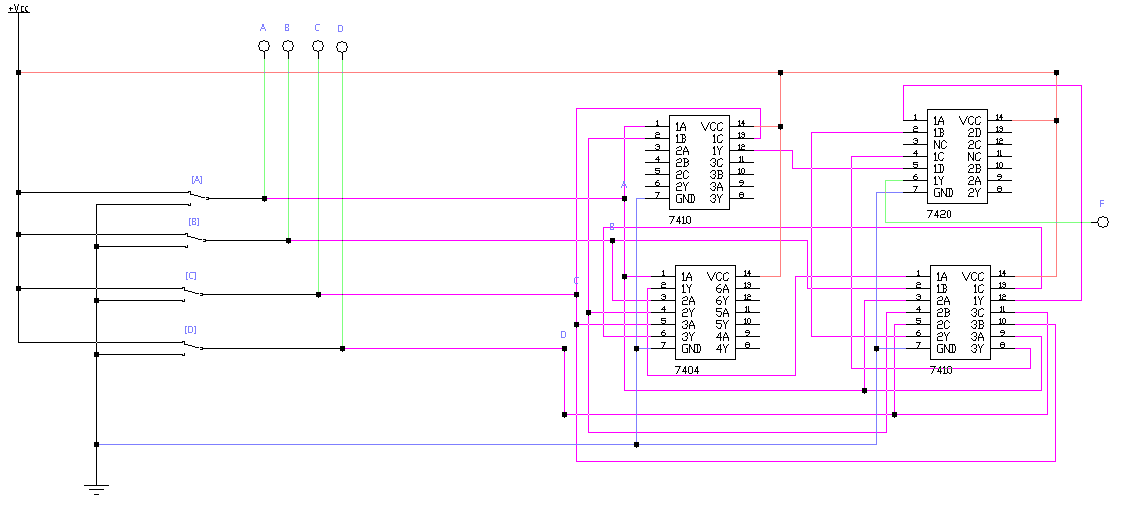

4. Электронная схема на основе микросхем

На базе имеющихся данных производится построение электронной схемы на основе микросхем (также по полученной схеме можно будет ориентироваться во время проектирования печатной платы).

Как можно заметить, в полученной электронной схеме использовано 4 микросхемы — 7404 (аналог К155ЛН1), 7410 (аналог К155ЛА4), 7410 (аналог К155ЛА4) и 7420 (аналог К155ЛА1). Для того чтобы понять, как происходит подключение, следует обратиться к фактическому изображению микросхем.

Сначала это может показаться сложным, но со временем вы поймете, что это не так уж и трудно.

ВАЖНО: не забывайте делать проверку.

Продолжение следует…

Абсолютно все цифровые микросхемы состоят из одних и тех же логических элементов – «кирпичиков» любого цифрового узла. Вот о них мы и поговорим сейчас.

Логический элемент – это такая схемка, у которой несколько входов и один выход. Каждому состоянию сигналов на входах, соответствует определенный сигнал на выходе.

Итак, какие бывают элементы?

Элемент «И» (AND)

Иначе его называют «конъюнктор».

Для того, чтобы понять как он работает, нужно нарисовать таблицу, в которой будут перечислены состояния на выходе при любой комбинации входных сигналов. Такая таблица называется «таблица истинности». Таблицы истинности широко применяются в цифровой технике для описания работы логических схем.

Вот так выглядит элемент «И» и его таблица истинности:

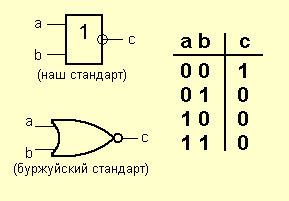

Поскольку вам придется общаться как с русской, так и с буржуйской тех. документацией, я буду приводить условные графические обозначения (УГО) элементов и по нашим и по не нашим стандартам.

Смотрим таблицу истинности, и проясняем в мозгу принцип. Понять его не сложно: единица на выходе элемента «И» возникает только тогда, когда на оба входа поданы единицы. Это объясняет название элемента: единицы должны быть И на одном, И на другом входе.

Если посмотреть чуток иначе, то можно сказать так: на выходе элемента «И» будет ноль в том случае, если хотя бы на один из его входов подан ноль. Запоминаем. Идем дальше.

Элемент «ИЛИ» (OR)

По другому, его зовут «дизъюнктор».

Любуемся:

Опять же, название говорит само за себя.

На выходе возникает единица, когда на один ИЛИ на другой ИЛИ на оба сразу входа подана единица. Этот элемент можно назвать также элементом «И» для негативной логики: ноль на его выходе бывает только в том случае, если и на один и на второй вход поданы нули.

Едем дальше. Дальше у нас очень простенький, но очень необходимый элемент.

Элемент «НЕ» (NOT)

Чаще, его называют «инвертор».

Надо чего-нибудь говорить по поводу его работы?

Ну тогда поехали дальше. Следующие два элемента получаются путем установки инвертора на выход элементов «И» и «ИЛИ».

Элемент «И-НЕ» (NAND)

Элемент И-НЕ работает точно так же как «И», только выходной сигнал полностью противоположен. Там где у элемента «И» на выходе должен быть «0», у элемента «И-НЕ» – единица. И наоборот. Э то легко понять по эквивалентной схеме элемента:

Элемент «ИЛИ-НЕ» (NOR)

Та же история – элемент «ИЛИ» с инвертором на выходе.

Следующий товарищ устроен несколько хитрее:

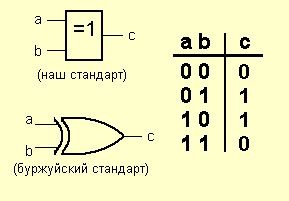

Элемент «Исключающее ИЛИ» (XOR)

Он вот такой:

Операция, которую он выполняет, часто называют «сложение по модулю 2». На самом деле, на этих элементах строятся цифровые сумматоры.

Смотрим таблицу истинности. Когда на выходе единицы? Правильно: когда на входах разные сигналы. На одном – 1, на другом – 0. Вот такой он хитрый.

Эквивалентная схема примерно такая:

Ее запоминать не обязательно.

Собственно, это и есть основные логические элементы. На их основе строятся абсолютно любые цифровые микросхемы. Даже ваш любимый Пентиум 4.

Далее мы позанудствуем о том, как синтезировать цифровую схему, имея ее таблицу истинности. Это совсем несложно, а знать надо, ибо пригодится (еще как пригодится) нам в дальнейшем.

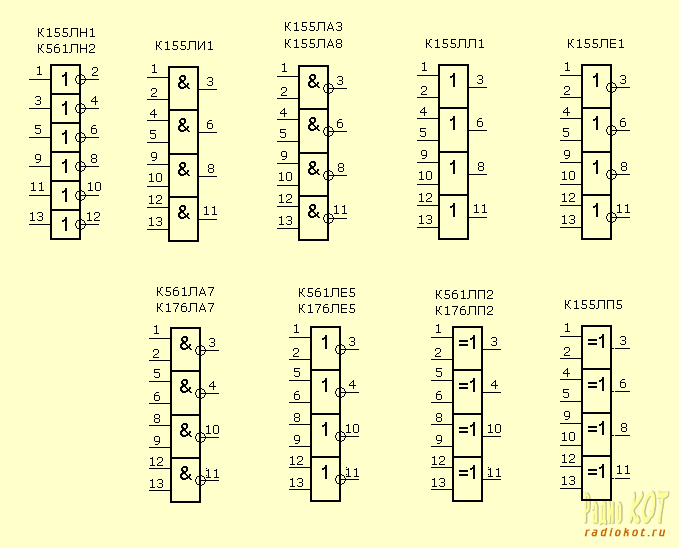

Ну и напоследок – несколько микросхем, внутри которых содержатся цифровые элементы. Около выводов элементов обозначены номера соответствующих ног микросхемы. Все микросхемы, перечисленные здесь, имеют 14 ног. Питание подается на ножки 7 (-) и 14 (+). Напряжение питания – смотри в таблице в предыдущем параграфе.

Источник: radiokot.ru

none

none

Опубликована: 2005 г.

Опубликована: 2005 г.

1

1

![]()

Вознаградить

Вознаградить

Я собрал

0

0

x

Оценить статью

- Техническая грамотность

- Актуальность материала

- Изложение материала

- Орфография

0

Средний балл статьи: 0

Проголосовало: 0 чел.