Рассказываем, как можно настроить оперативную память компьютера и для чего это вообще может понадобиться.

Как вообще можно настроить оперативную память?

Начнем с краткого ликбеза. Разберемся, какие параметры ОЗУ можно изменить и для чего это нужно (или не нужно) делать. Есть такой термин как «латентность оперативной памяти», ее еще иногда называют таймингом. Это временная задержка сигнала при работе ОЗУ со страничной организацией. Именно такой вариант организации памяти и задействован в компьютерах.

Вдаваться в технические подробности не будем, но если описывать ситуацию вкратце, то от показателей латентности зависит пропускная способность участка, отвечающего за обращение чипа к оперативной памяти. Чем ниже тайминг, тем выше производительность памяти. Ну и компьютера в целом.

Раньше это значение играло очень важную роль, так как у процессоров был низкий объем кэша и они очень часто обращались к оперативной памяти. В нынешних чипах кэш настолько увеличился, что иногда обращения к ОЗУ не происходит вовсе. Поэтому сейчас в оперативной памяти куда больше ценится частота и объем. Именно от них зависит скорость работы операционной системы, игр и так далее.

Тем не менее небольшую прибавку получить всегда приятно, да и привычка «ускорять» ОЗУ до сих пор осталась. Поэтому мы и рассказываем, как это можно реализовать.

Настраиваем ОЗУ

Процедура настройки оперативной памяти выглядит по-разному в зависимости от используемой версии BIOS. При этом изменяемые параметры всегда идентичны. Разница в том, как к ним можно добраться. Разберем три ключевые версии BIOS.

Не вносите кардинальных изменений в латентность и вольтаж. Они играют важную роль в работе компьютера и неосторожное действия со стороны пользователя могут физически вывести из строя оперативную память или другие компоненты устройства. Все изменения вы применяете на свой страх и риск. Действуйте осторожно.

Настройка для BIOS компании Award

Вот, что нужно делать, если вы используете материнскую плату с Award BIOS (или Phoenix).

- Перезагружаем компьютер (или включаем его, если еще этого не сделали). Заходим в BIOS, нажав на соответствующую клавишу.

- После того, как перед вами появится синий экран с параметрами компьютера, одновременно нажимаем на клавиши Ctrl + F1. Это откроет дополнительные настройки.

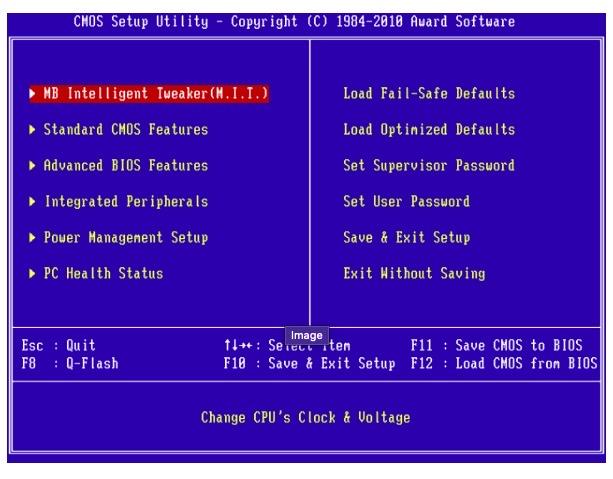

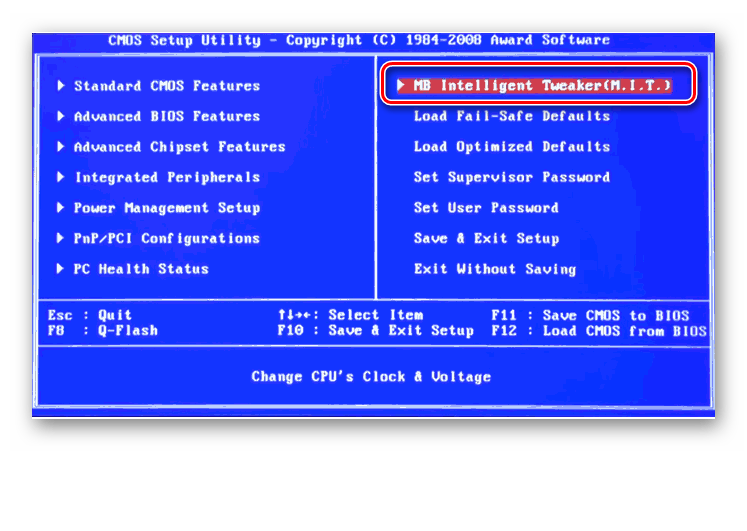

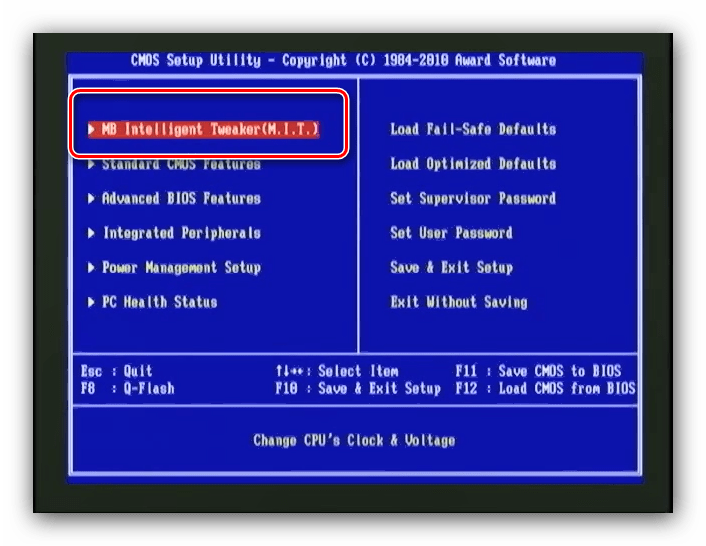

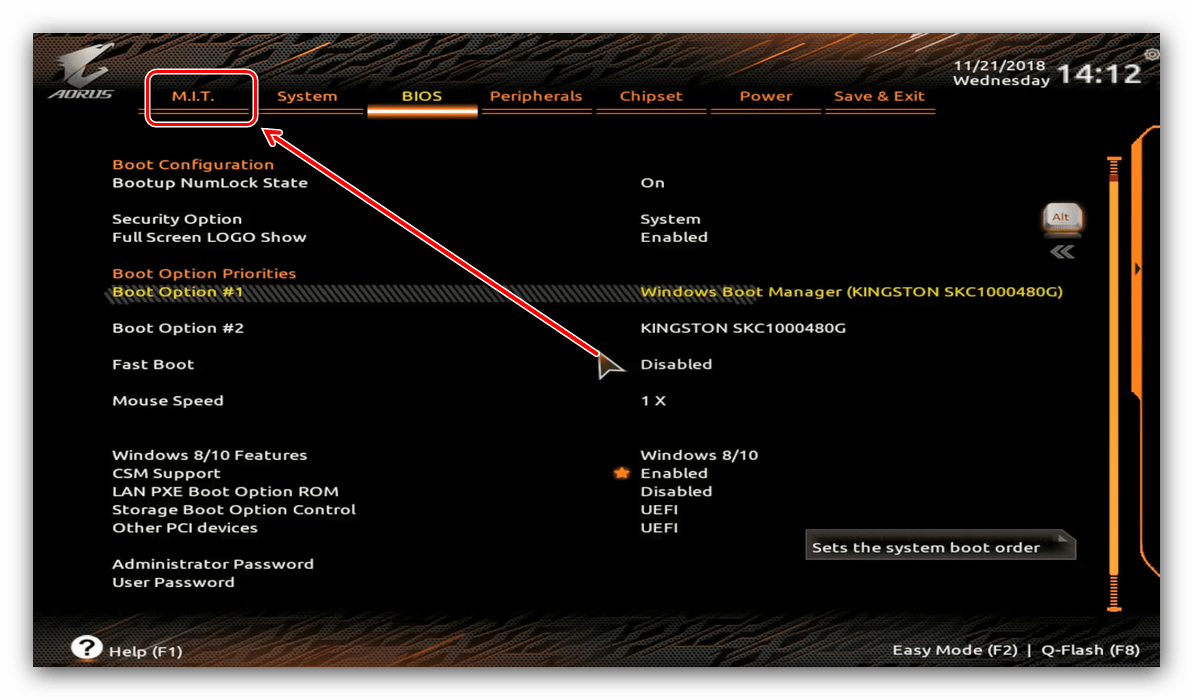

- В появившемся списке опций ищем строчку MB Intelligent Tweaker (M.I.T.), выделяем ее с помощью клавиш-стрелок и нажимаем на «Ввод» (Enter).

Иногда эта строчка появляется в правой панели

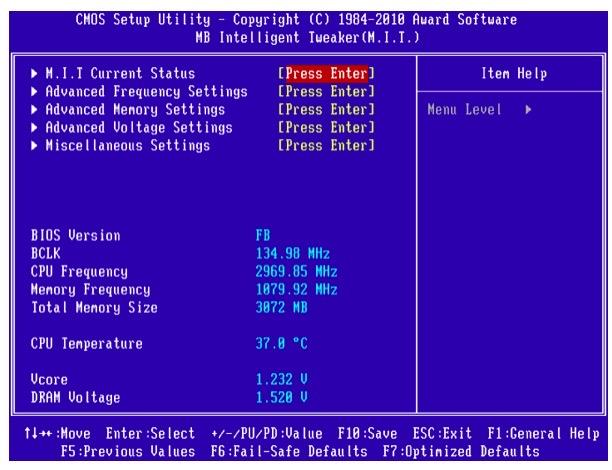

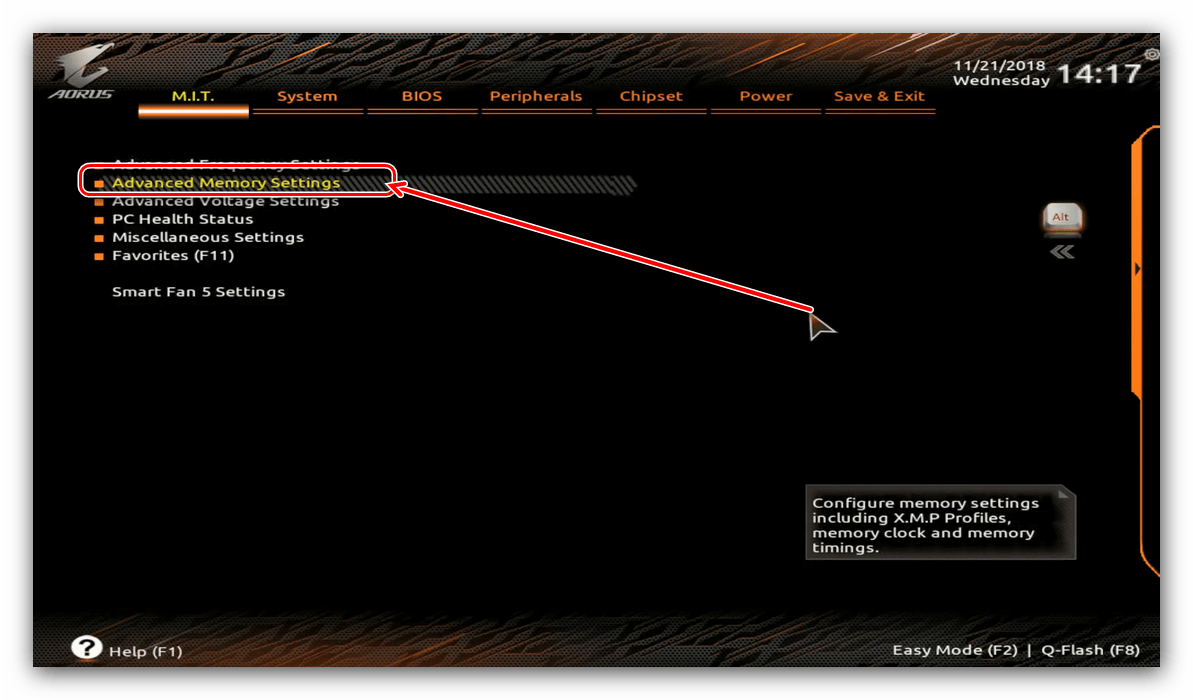

- Далее ищем раздел Advanced Memory Settings и переходим в него.

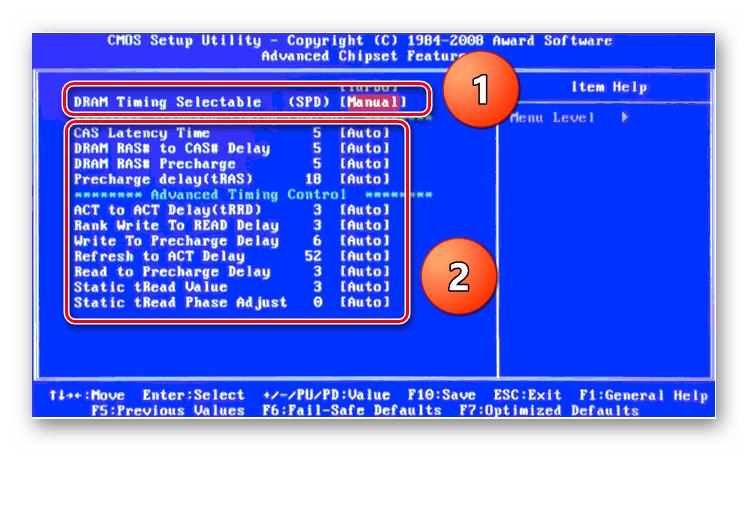

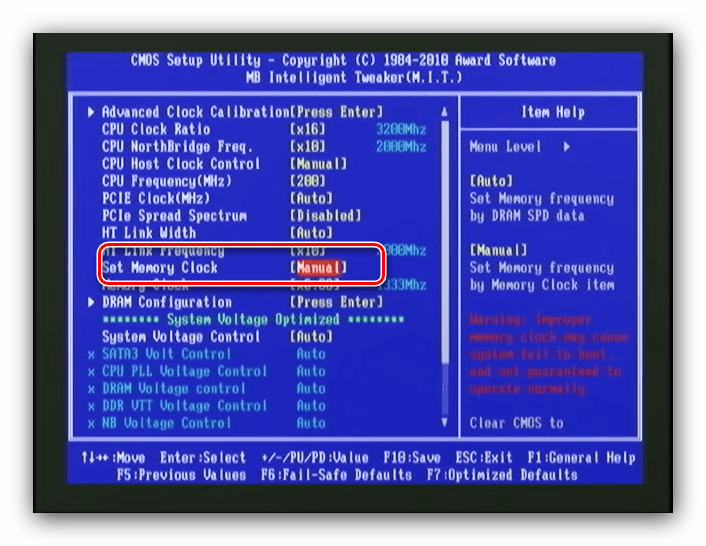

Здесь мы и будем вносить изменения

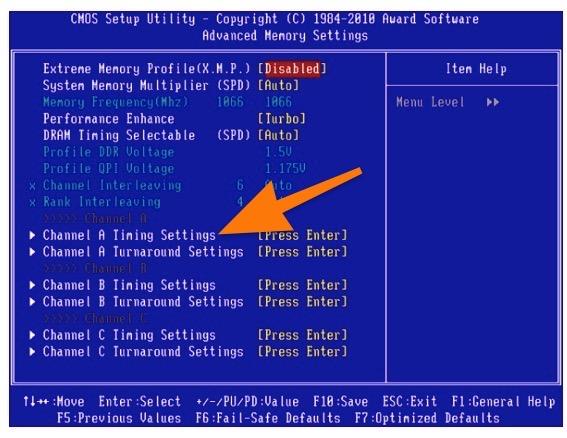

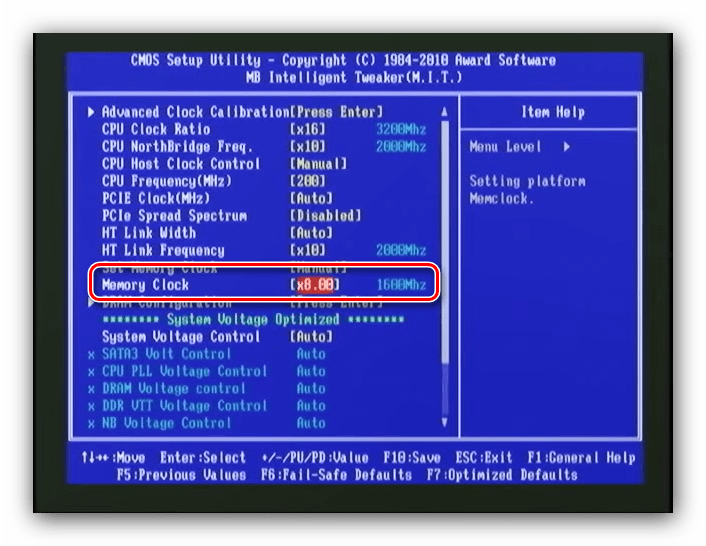

- После этого ищем канал памяти, тайминг в котором нужно изменить. Выделяем его с помощью клавиш стрелок и нажимаем «Ввод».

Выбираем канал

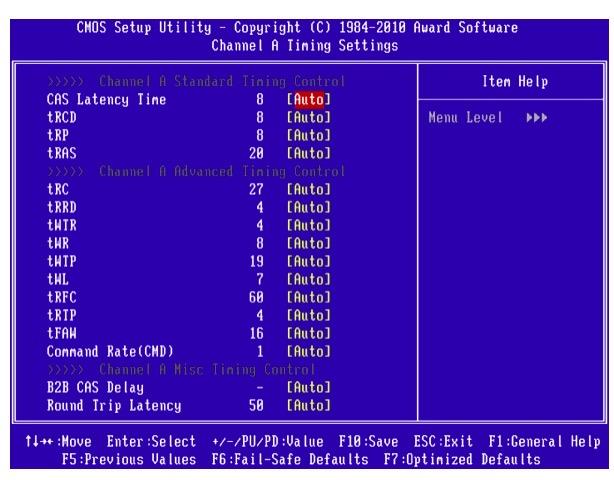

- В открывшемся меню ищем латентность, которую хотим поменять и переключаем режим в ручное управление (нажав «Ввод»).

Каждый пункт здесь — определенный параметр латентности, который можно скорректировать

В некоторых версиях Award BIOS нужно действовать иначе.

- Открываем BIOS.

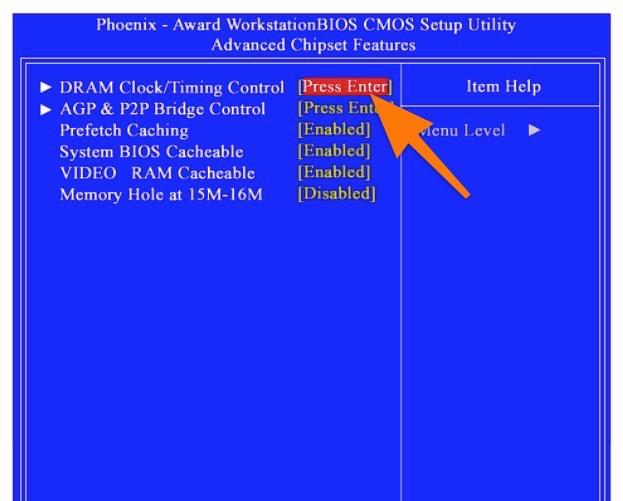

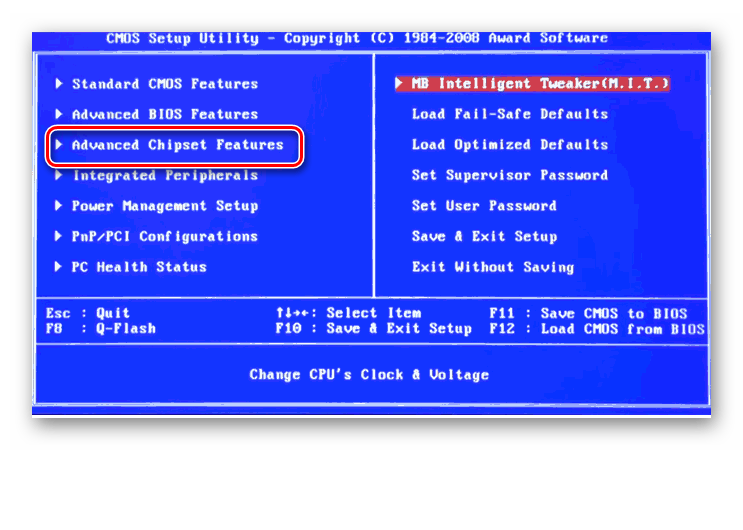

- Переходим в раздел Advanced Chipset Features.

- Затем входим в подменю DRAM Clock/Timing Control.

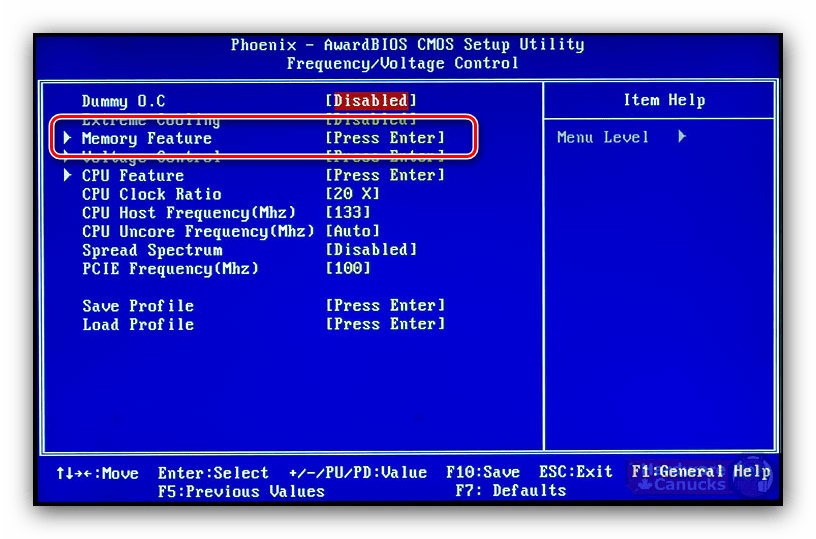

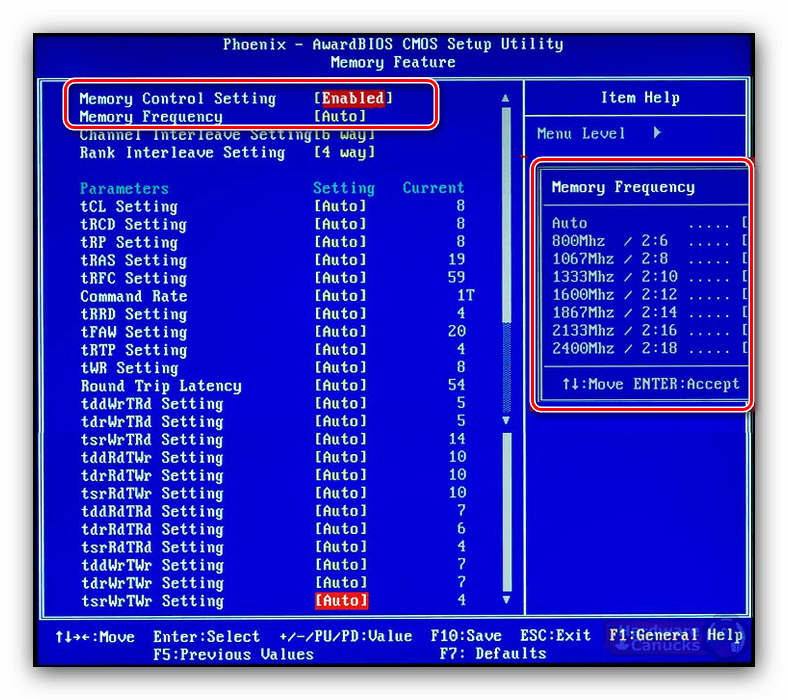

Нужный пункт

- Настраиваем тайминг ОЗУ с учетом своих предпочтений. Узнать о свойствах каналов и особенностях тайминга можно из официальной документации производителя вашего «железа».

Отдельно стоит упомянуть возможность увеличения подачи тока на отдельные комплектующие. В том числе и память. Для этого:

- Открываем BIOS.

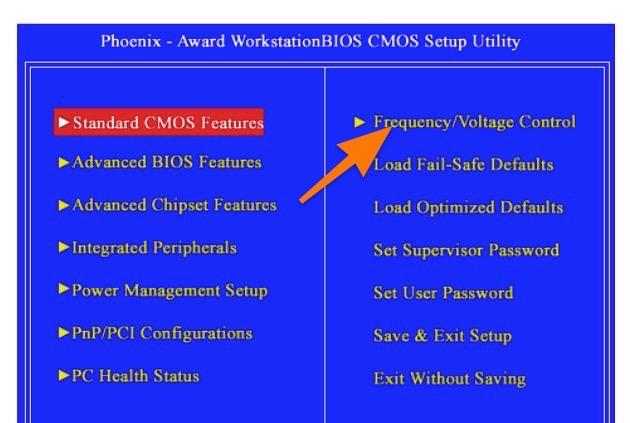

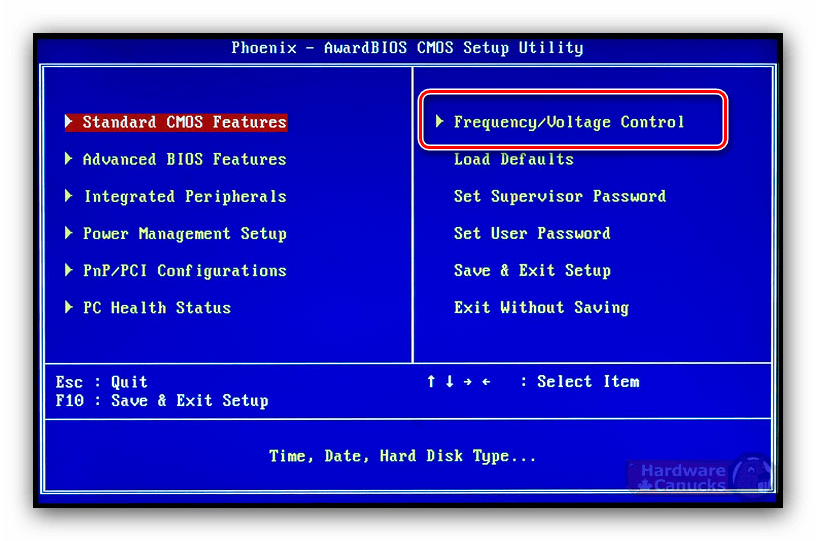

- Переходим в меню Frequency/Voltage Settings.

Иногда этот пункт прячется в меню M.I.T.

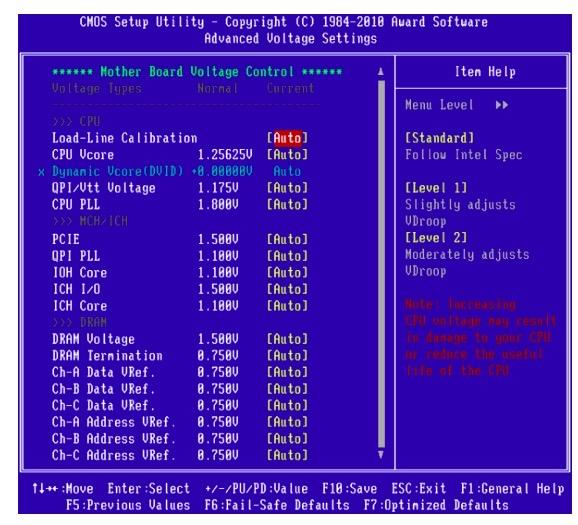

- Меняем показатели DRAM Voltage в соответствии со своими предпочтениями.

Изменения более чем на 0.15 единиц могут быть критичны для компьютера

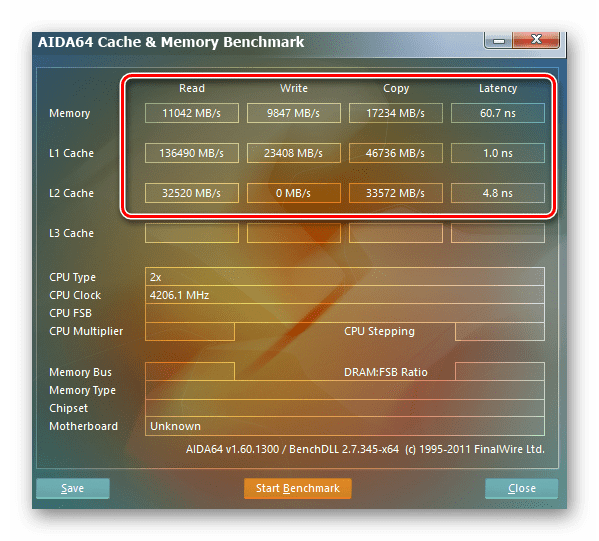

После внесения изменений нужно проверить периферию компьютера с помощью специального программного обеспечения. Например, AIDA64. Там есть специальный режим для оценки состояния памяти и стабильности системы.

Настройки для BIOS AMI

Интерфейс в BIOS компании Amerian Megatrends сильно отличается. Мало того, что он сложнее, так он еще имеет кучу вариаций. Поэтому зачастую тяжело наверняка сказать, где в нем находятся те или иные настройки.

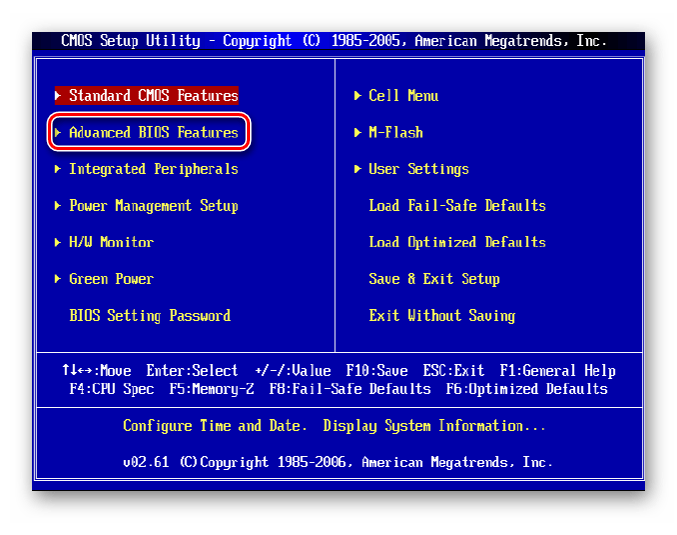

В некоторых вариациях на главной странице есть пункт Advanced BIOS Features.

- Выбираем этот пункт.

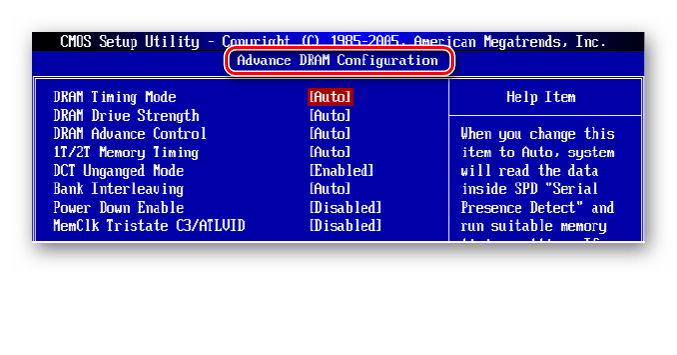

- Затем переходим в подменю Advance DRAM Configuration.

- Внутри переводим опцию DRAM Timing Mode в ручной режим управления и меняем значения латентности.

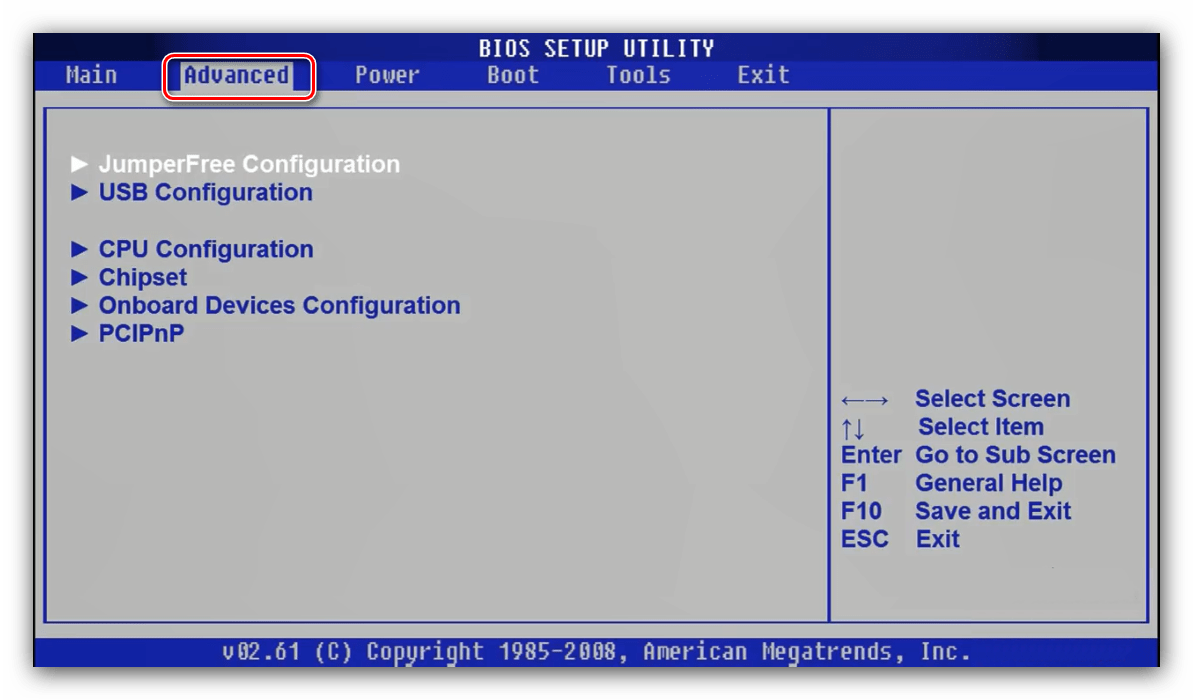

Есть и другая версия BIOS, интерфейс которой построен на вкладках в верхней части экрана. Там нужная опция может прятаться сразу в нескольких местах:

- Основная вкладка (пункт имеет схожее с предыдущим вариантов название).

- Вкладка Advanced, где хранится ряд настроек процессора.

- Вкладка PCI, где хранится информация и настройки для устройств, подключенных через PCI-разъемы.

Придется покататься во всех разделах самостоятельно, пока не наткнетесь на пункт управления оперативной памятью. Пункт будет называться как-то в духе DRAM Timings…

Впрочем, надо отметить, что у Award/Phoenix есть версии BIOS с дизайном, который очень сильно напоминает AMI. Поэтому у вас может быть интерфейс на вкладках даже в случае с совершенно иным поставщиком ПО для материнской платы.

Остальные опции и параметры будут идентичны.

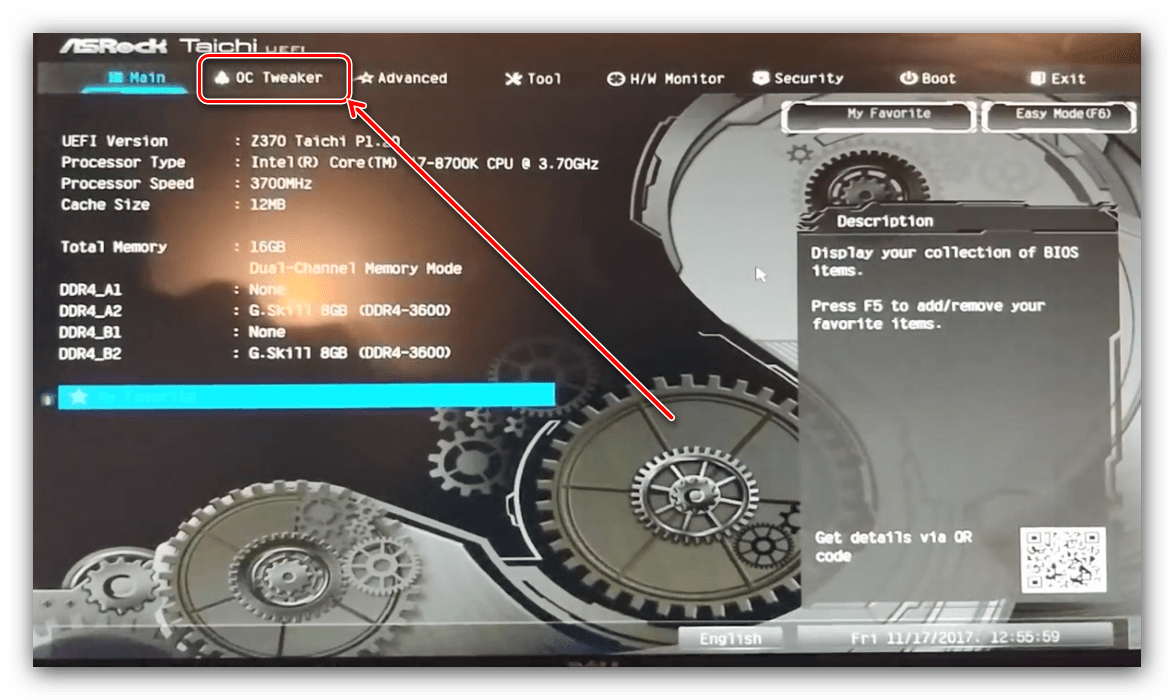

Настройка для UEFI

В UEFI все устроено примерно так же. Чтобы настроить в нем оперативную память:

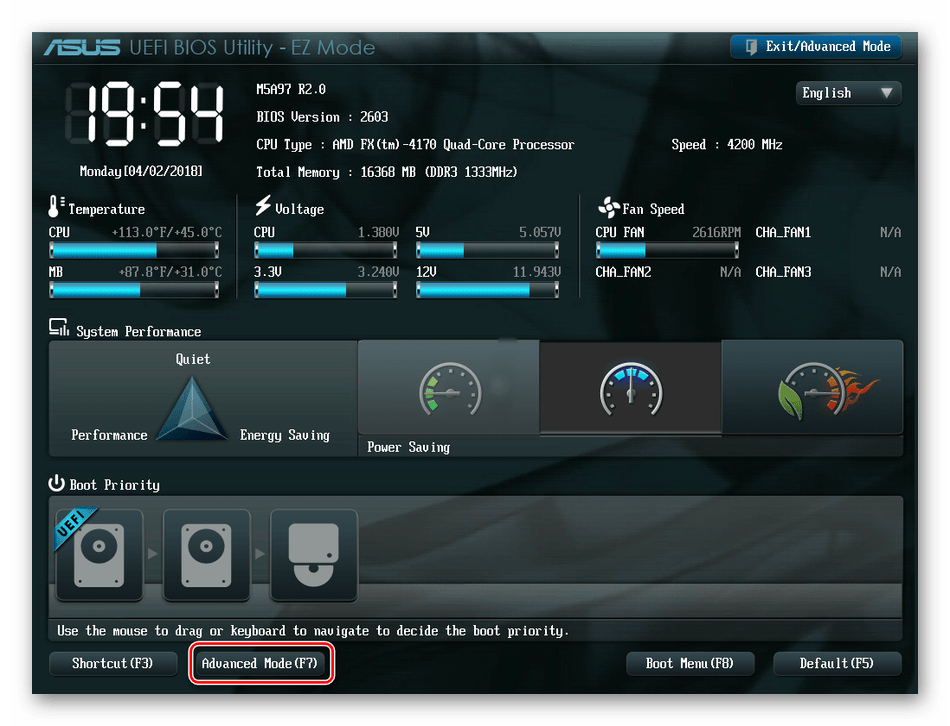

- Открываем BIOS, нажав на соответствующую клавишу во время загрузки компьютера.

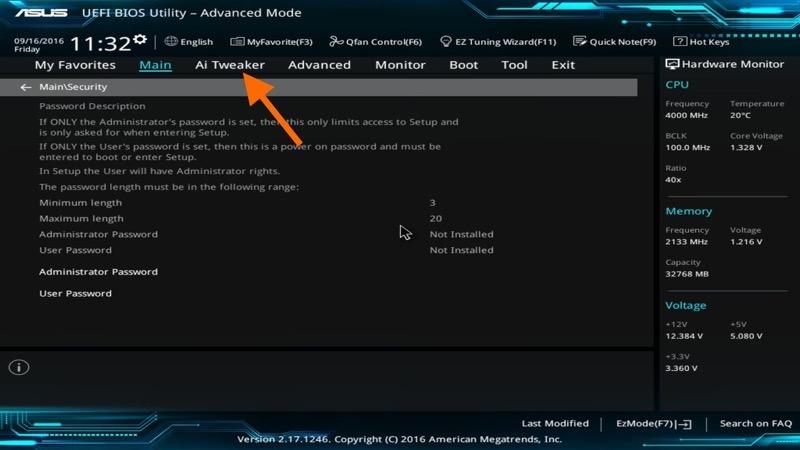

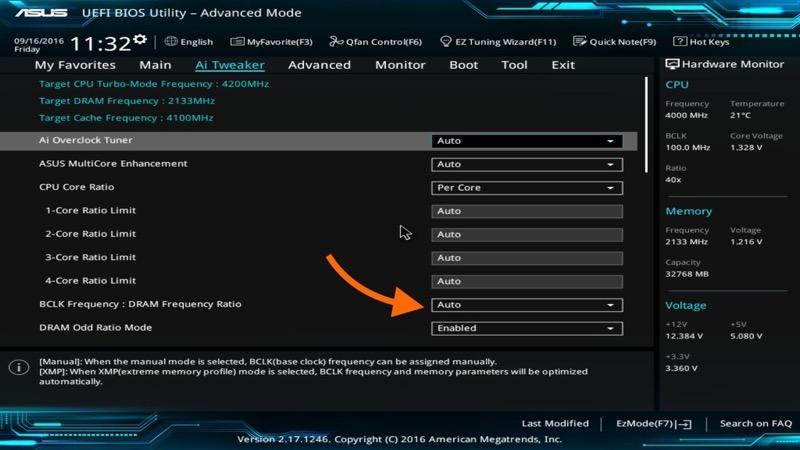

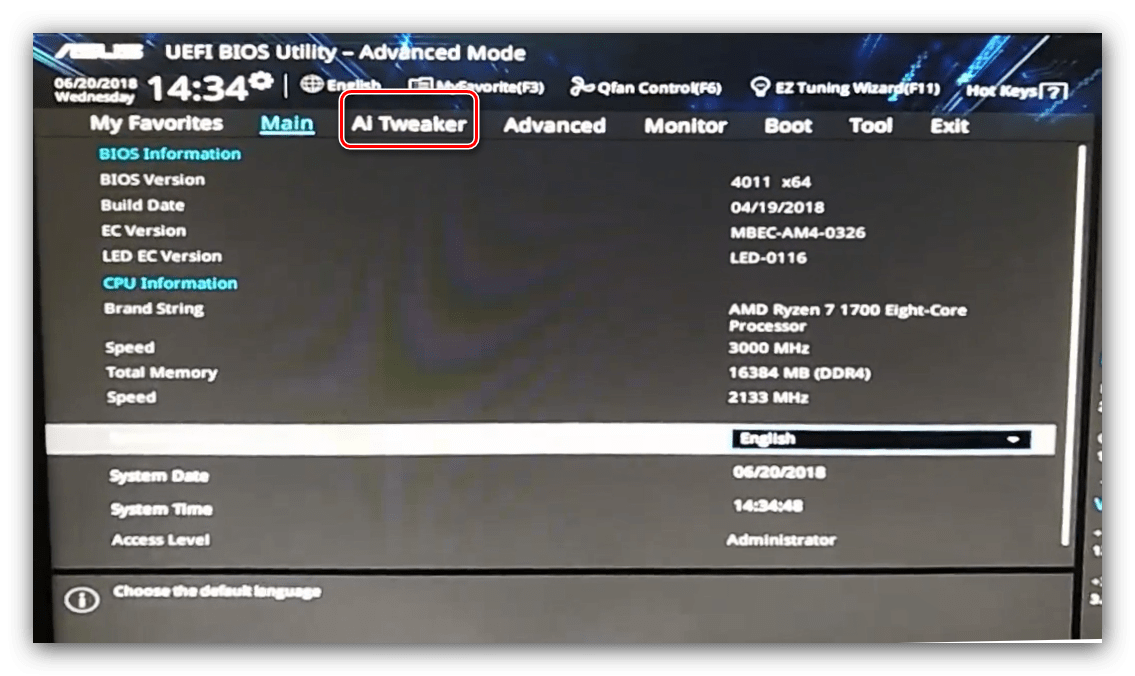

- Оказавшись в UEFI BIOS Utility, кликаем (да, тут доступна мышь) по вкладке Ai Tweaker.

Вот и нужный пункт

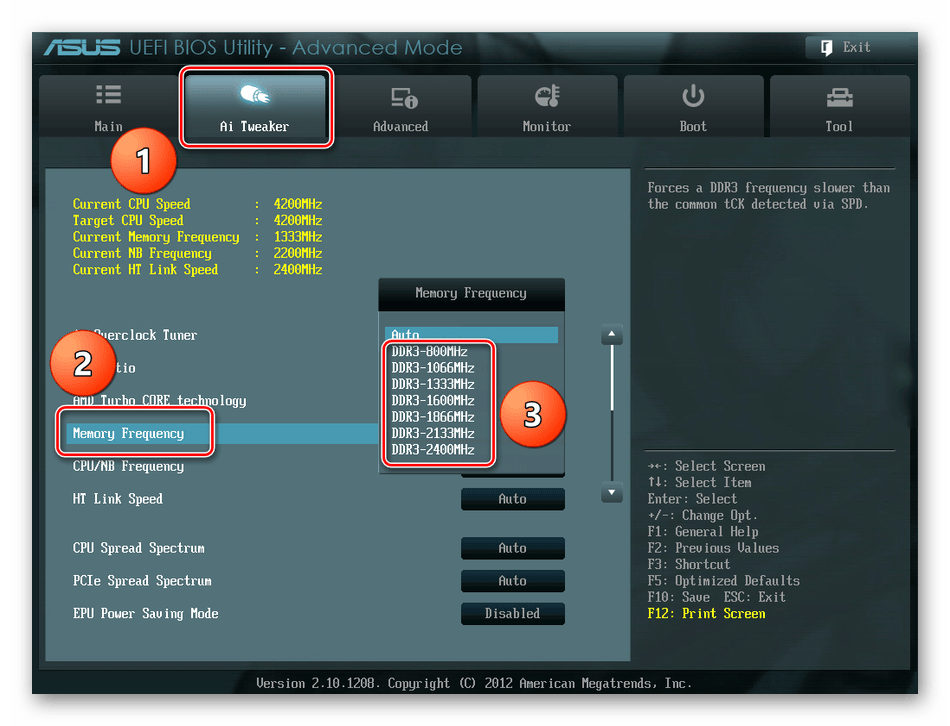

- В открывшемся меню ищем пункт BCLK Frequency: DRAM Frequency Ratio и кликаем по кнопке справа от него.

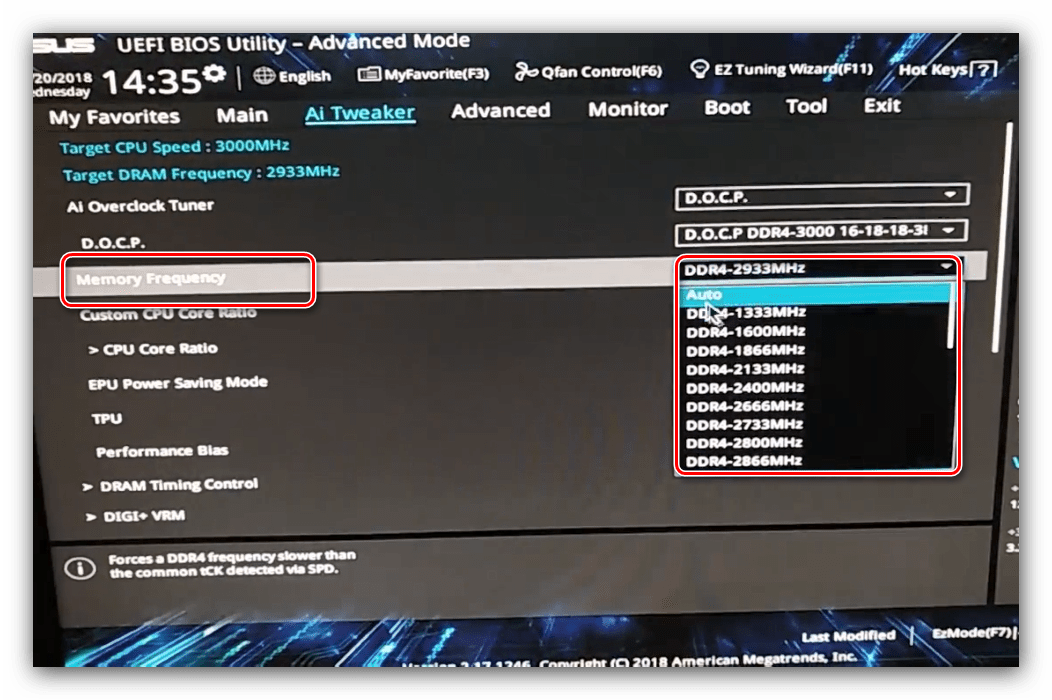

- Появится список всех доступных частот оперативной памяти. Выбираем ту, что нам подходит.

Оптимально выбирать самую высокую частоту, доступную для вашей модели RAM

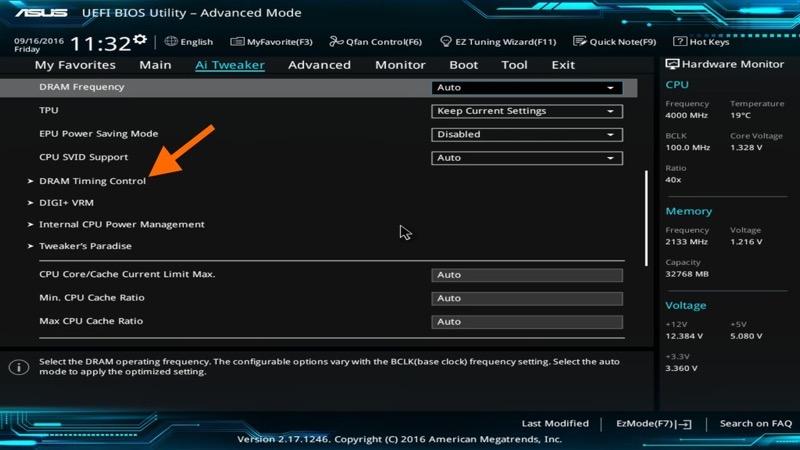

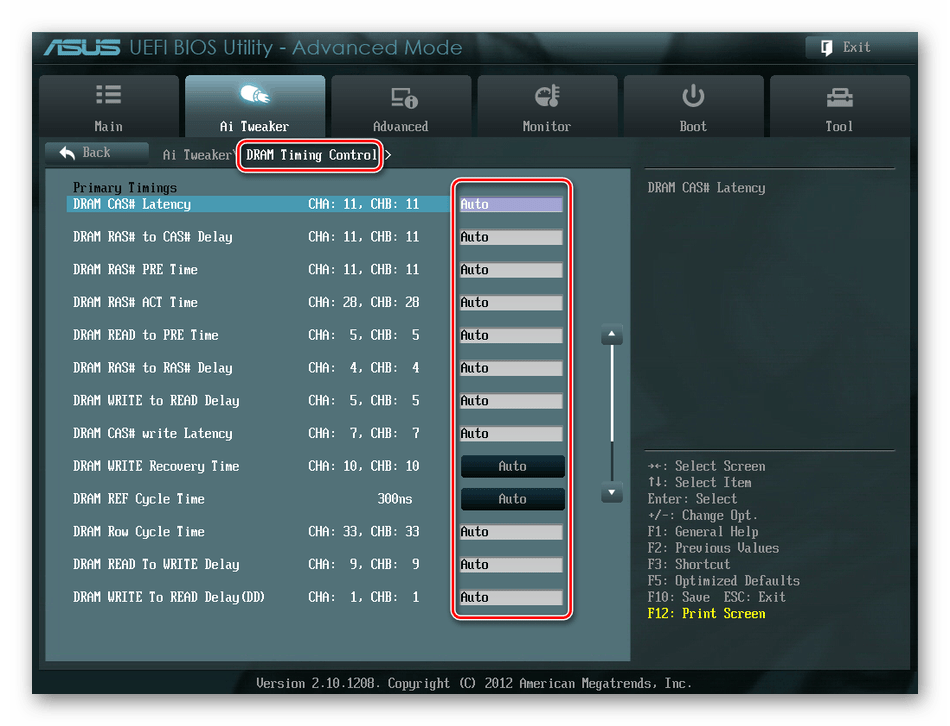

- Затем возвращаемся на предыдущий экран и кликаем по строчке DRAM Timing Control.

Переходим к следующему пункту…

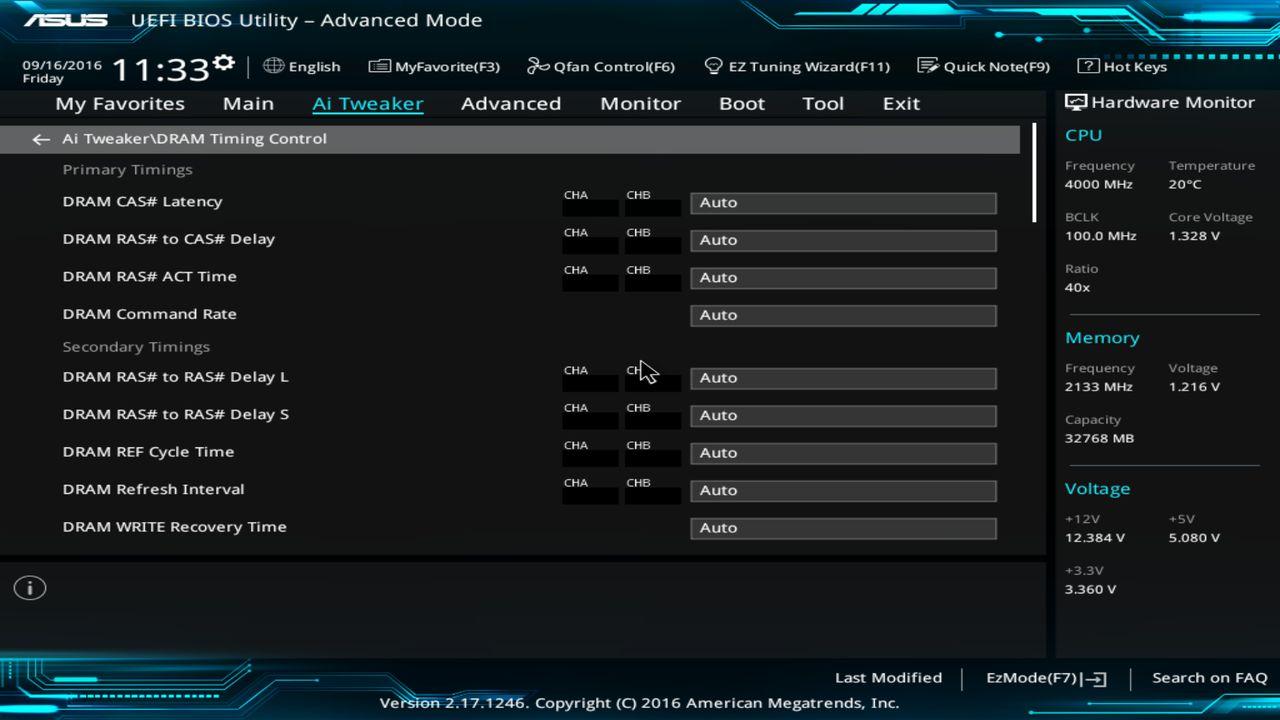

- Перед нами появятся все доступные параметры таймингов. Настраиваем их на свое усмотрение.

Здесь доступны те же опции, что и в других версиях BIOS

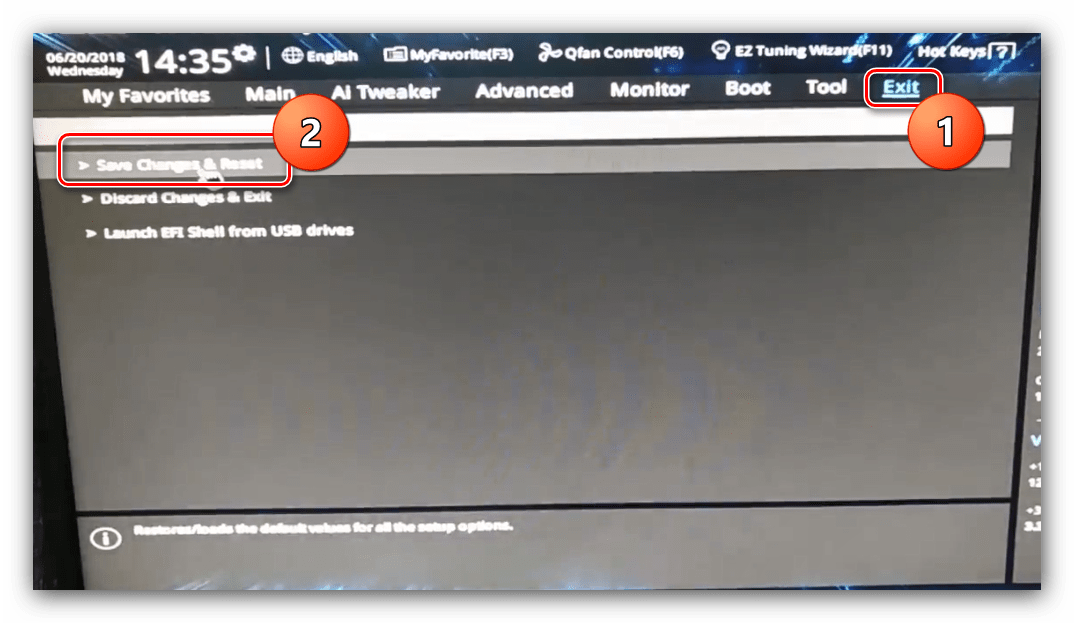

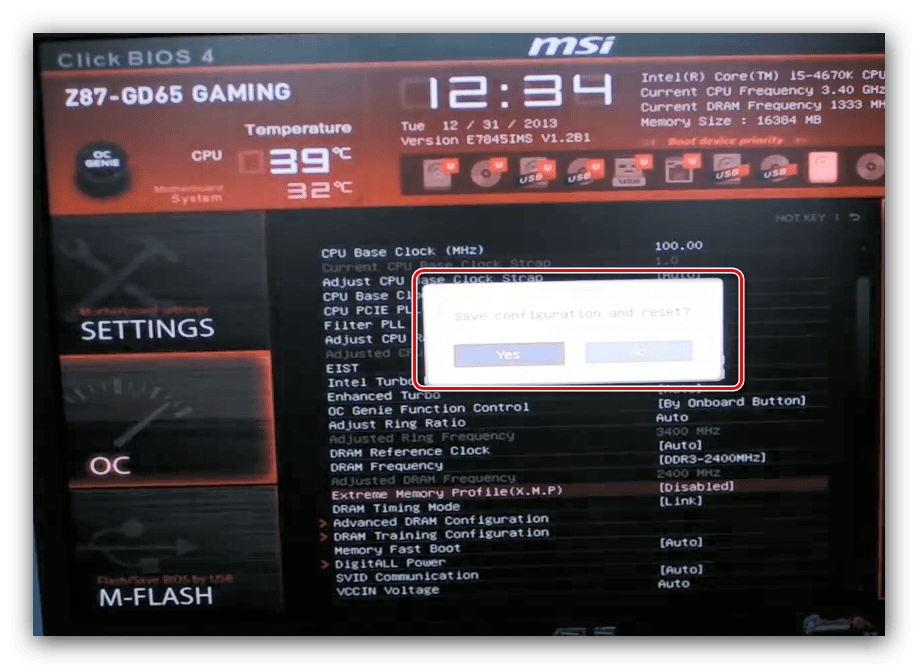

- В конце просто сохраняем настройки и закрываем BIOS.

Опять же. Не забудьте протестировать оперативную память после изменения настроек. Нужно сразу фиксировать любые негативные последствия, чтобы не допустить серьезной поломки.

Post Views: 14 589

Если говорить об оперативной памяти или, как ее еще называют, оперативном запоминающем устройстве (ОЗУ) в контексте работы в рамках компьютерной системы, то все ее параметры задаются непосредственно самой операционной системой Windows и БИОСом. Конечно, на работу плашек данной памяти влияет и ее самостоятельные конфигурации, поэтому невозможно через компьютер задать режим работы, который в значительной мере отличается от предусмотренного изготовителем. Но несмотря на это, пользователь может самостоятельно вносить корректировки в работу этого элемента, например, разогнать ОЗУ.

В этой статье будет рассказано, как произвести настройку оперативной памяти в БИОСе. Дочитайте статью до конца, так как, помимо основной инструкции, речь будет вестись о смежных вещах, без знания которых может ничего не получиться.

Почему может не получиться настроить оперативную память в БИОСе

К сожалению, каждый пользователь не может вносить коррективы в настройки оперативной памяти. И обусловлено это совсем не ее моделью, поэтому не нужно гадать, какая оперативная память лучше подходит для корректировки параметров. Напротив, связано это с моделью материнской платы. Почему? Да потому, что BIOS Setup Utility находится именно в ней. Отсюда выходит, что первым делом необходимо понять, позволяет ли комплектация компьютера вносить изменения в настройки ОЗУ. А сделать это не так уж и просто, ведь каждая материнская плата отличается друг от друга, но точно можно сказать, что старые платы и платы низшего ценового сегмента стопроцентно не подходят.

Контроллер PCI

CPU to PCI Write Buffer — когда процессор работает с PCI-устройством , он производит запись в порты. Данные при этом поступают в контроллер шины и далее в регистры устройства.

Если мы включаем эту опцию, задействуется буфер записи, который накапливает данные до того, как PCI-устройство будет готово. И процессор не должен его ждать — он может выпустить данные и продолжить выполнение программы. Я советую Вам включить эту опцию.

PCI Dynamic Bursting — этот параметр также связан с буфером записи. Он включает режим накопления данных, при котором операция записи производится только тогда, когда в буфере собран целый пакет из 32 бит. Включать обязательно.

PCI Latency Timer – параметр устанавливает количество тактов, отводимых каждому PCI-устройству на осуществление операции обмена данными. Чем больше тактов, тем выше эффективность работы устройств. Однако при наличии ISA-устройств данный параметр нельзя увеличивать до 128 тактов.

Запуск BIOS Setup Utility

Что нужно сделать в первую очередь? Несомненно, прежде чем приступать к настройке оперативной памяти, необходимо войти в CMOS. Что это? Это и есть тот самый БИОС. К сожалению, предложить универсальный способ входа в него невозможно, ведь все зависит непосредственно от производителя и самой материнской платы. Но можно сказать, что вход осуществляется непосредственно при запуске компьютера, когда перед вами много разных слов на фоне черного экрана. В этот момент вам необходимо нажать специальную клавишу, отвечающие за вход в утилиту BIOS. Чаще всего это Del, реже F1 или F2. Это что касается компьютеров, у ноутбуков, наоборот, для входа используются клавиши с приставкой F (F1, F2, F10, F11 или F12).

Вообще, вы можете увидеть необходимую клавишу в момент загрузки системы, там будет примерно следующий текст: «Press DEL to run Setup», где вместо «DEL» будет указана, возможно, другая клавиша.

Немного теории

Без оперативной памяти, которую разработчики первых вычислительных машин называли «складом информации», сегодня невозможно функционирование ни одного компьютера. За период существования настольных ПК она проделала сложный путь от простейших микросхем, распаянных по материнской плате, до высокотехнологичного съемного модуля. В настоящее время устанавливаются преимущественно ОЗУ стандартов DDR2, DDR3 и DDR4. У каждого из них частота памяти и шины данных выше, чем у предыдущего.

Помимо частоты, важнейшим показателем RAM-памяти является ее емкость. Она измеряется в гигабайтах и лежит, как правило, в пределах 2-16 Гб. Модули «оперативки» устанавливаются в соответствующие разъемы на материнской плате, которых обычно два или четыре. У ноутбуков и полноразмерных компьютеров размеры и конфигурация разъемов отличаются – это необходимо учитывать при замене или увеличении объема ОЗУ.

Интерфейс BIOS

Итак, мы не только разобрались, что CMOS – это и есть БИОС, но и, что немаловажно, мы решили, как в него войти. Однако переходить к руководству по изменению параметров оперативного запоминающего устройства все равно рановато, ведь для начала необходимо разобраться в разновидностях БИОСа, а точнее, в разновидностях его интерфейсов.

Забегая вперед, скажем, что в статье будут разобраны три представителя: AMI, UEFI и AWARD, хотя есть еще Intel BIOS, но это лишь модификация AMI, поэтому инструкция для них общая. Стоит также не путать AWARD BIOS и Phoenix, так как это одно и то же.

Все вышеперечисленные версии имеют разный внешний вид, из-за чего настройка оперативной памяти в БИОСе выполняется по-разному. Описывать каждый сейчас нет смысла, ведь далее все будет дословно изложено. Стоит лишь сказать одно – несмотря на отличный друг от друга внешний вид и разное расположение некоторых элементов интерфейса, инструкция во многом применима для всех BIOS Setup Utility.

Способ №2. При помощи различных программ

Плюс данного способа в том, что вы получите кучу информации о своем компьютере и все это в одном месте. Ну а минус в том, что это не стандартное средство, которое идет в комплекте с windows. В любом случае для домашнего использования данный вариант хорошо подходит. Но вот если ваша работа потребовала от вас узнать сколько оперативной памяти да и не только оперативной, то пользоваться придется стандартными средствами. В принципе с их помощью можно многое узнать. Но на мой взгляд стороннее ПО будет намного лучше для этих целей, поскольку разработчики сделали все, чтобы обеспечить удобство пользования. К примеру, продиагностировав компьютер, результат можно сохранить в текстовый файл или какой-нибудь другой формат. Во многих программах для диагностики компьютера такая функция присутствует.

Aida64 Extreme

Одна из лучших на мой и не только мой взгляд программа для диагностики. Дает очень подробную характеристику вашего компьютера.

Скачать

Speccy

Тоже неплохая программа, удобная и бесплатная. Есть portable версия у Aida64 вроде бы такого нет. Здесь не слушайте меня, ибо я не в курсе. Могу сказать лишь то, что удобна и лаконична.

Скачать

Настройка

Вот теперь, разобравшись со всеми нюансами, выяснив, что такое CMOS и как войти в БИОС, наконец-то мы можем перейти непосредственно к руководству по тому, как произвести настройку оперативной памяти. Однако учтите, что вмешательство в параметры этого компонента может повлиять на стабильность работы компьютера. Этот «показатель» может измениться как в лучшую сторону, так и в худшую, поэтому рекомендуется иметь за плечами большую теоретическую базу знаний, чтобы в процессе выполнения всех указаний не причинить вред компьютеру.

Что нужно изменять?

При разгоне или понижении работоспособности RAM следует обращать внимание на следующие несколько пунктов:

- Тактовая частота. Тактовая частота – это количество операций, которые совершает оперативная память в один такт. Увеличение данного значения существенно улучшит работу вашей оперативной памяти.

- Тайминги. Тайминги – это набор цифр, которые, помимо БИОСа, Вы можете обнаружить и на самих планках оперативной памяти. Чем ниже значения данных цифр, тем быстрее ЦП получает данные от RAM.

- Напряжение памяти. Напряжение памяти – это напряжение, которое получает RAM от блока питания. Любые другие значения мы категорически не рекомендуем их как-либо изменять, так как из-за этого может выйти из строя вся система ПК без возможности восстановления.

Все эти изменения – как лотерея. Точных и совершенно правильного алгоритма для всех не существует, Если Вы хотите изменить память в БИОСе, то нужно будет менять каждое значение на одну единицу, после чего смотреть на результат. В противном случае, Вы рискуете полностью «спалить» оперативную память либо сломать весь компьютер.

Также не рекомендуем сильно «разгонять» RAM, так как даже в случае корректной работы, через некоторое длительное время этот аппаратный компонент придет в негодность из-за того, что работал на мощности, не предназначенной для него.

Способ первый: Award BIOS

А начнем мы с того, что расскажем, как настроить оперативную память в БИОСе Award. Этот вид CMOS отличается раздельным экранном, поделенным на две части. В левой – стандартные настройки, а в правом – расширенные. задействовать мы будем и те и другие. Ну, долго не разглагольствуя, перейдем к самой инструкции по настройке.

- Войдя в БИОС Award, нажмите сочетание клавиш Ctrl+F, чтобы получить доступ к расширенной настройке.

- Используя стрелочки на клавиатуре, выделите строку «MB Intelligent Tweaker».

- Нажмите клавишу Enter для входа в меню настроек этого параметра.

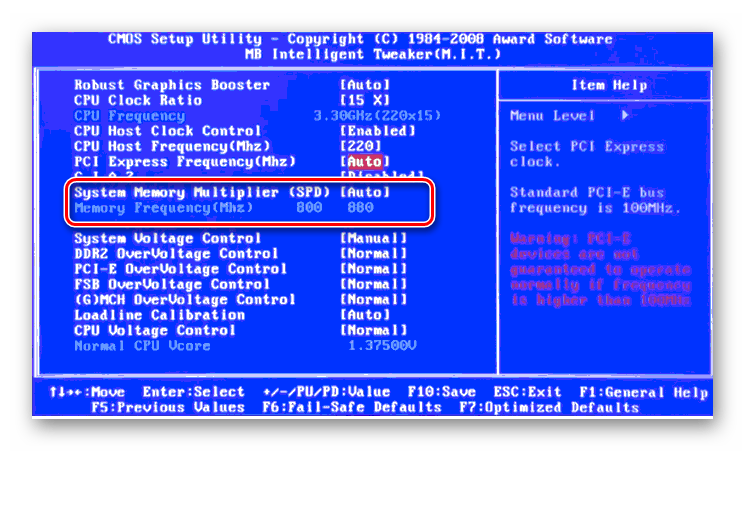

- Здесь вы можете увеличить или, наоборот, уменьшить тактовую частоту своей оперативной памяти. Делается это путем изменения параметра «System Memory Multiplier». Однако учтите, что изменять показатель до максимального значения нельзя, это может привести как к сбоям в работе компонента, так и вовсе к полной его поломке. Желательно выбирать значение чуть больше изначально указанного.

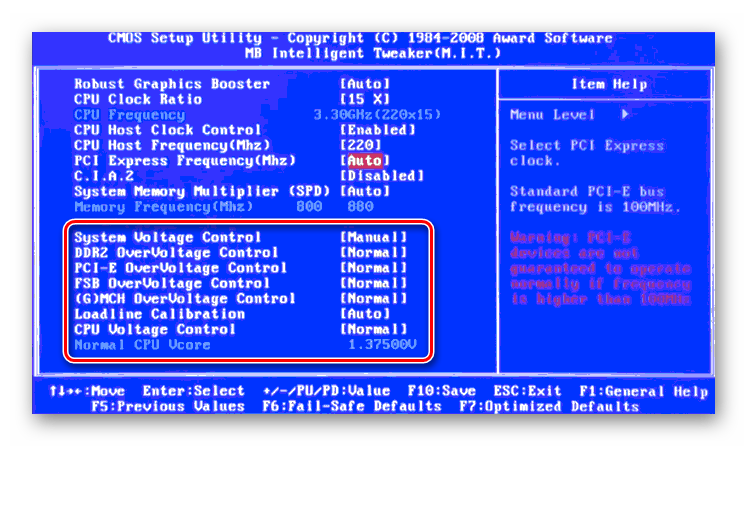

- Здесь же вы можете изменить напряжение подаваемого тока на ОЗУ, делается это в нижней части экрана. Но и тут есть ограничения, крайне не рекомендуется менять его более чем на 0,15 В.

- Вернитесь в главное меню, нажав Esc.

- Выберите пункт «Advanced Chipset Features» и перейдите в него.

- Здесь вам позволят поменять время отклика ОЗУ. Для начала измените пункт «DRAM Timing Selectable» на «Manual», а затем приступайте к смене значений.

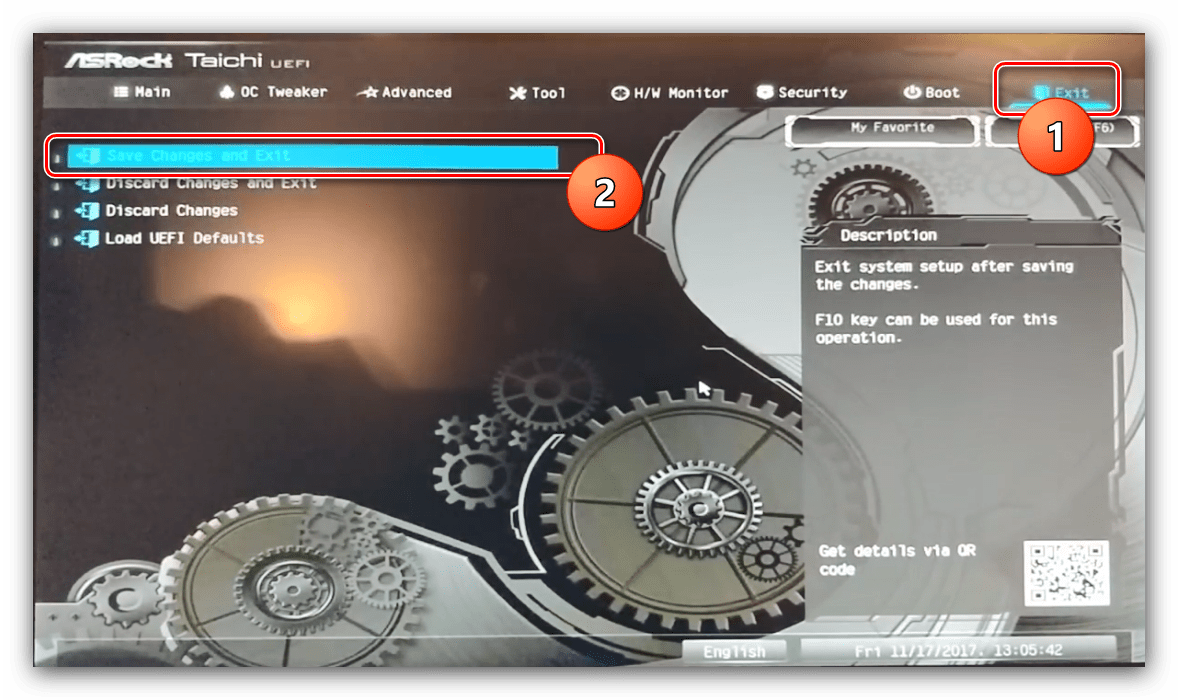

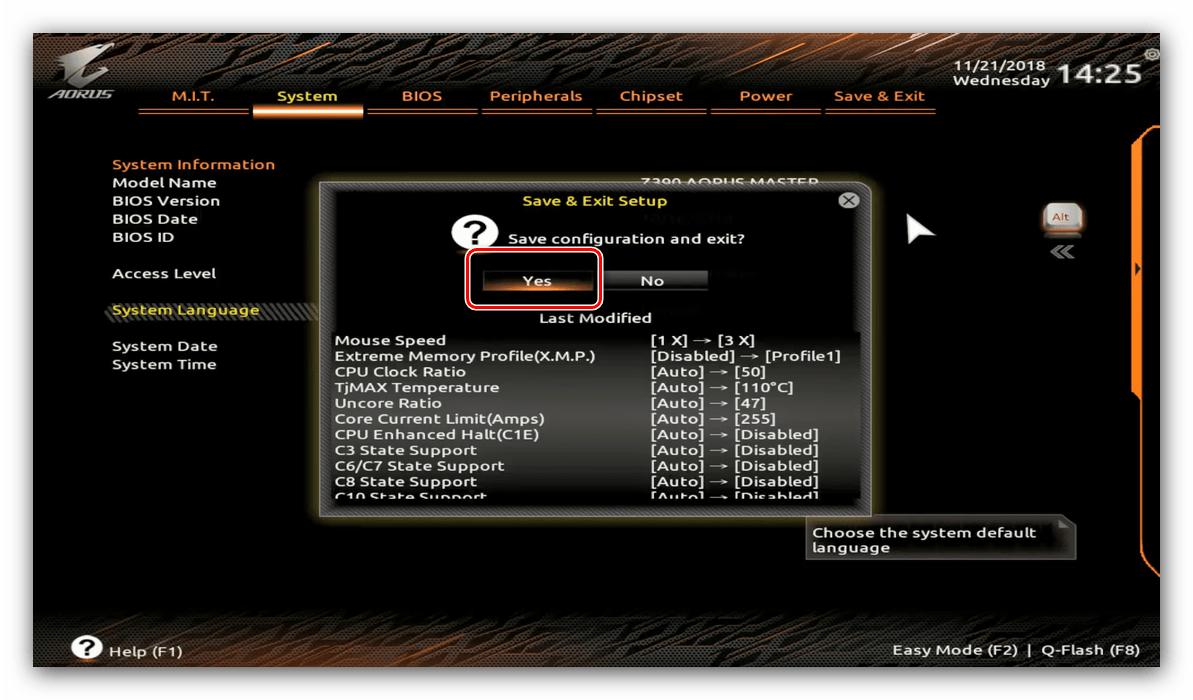

На этом настройку можно считать оконченной, нажмите F10 для сохранения всех изменений и выйдите из БИОСа.

Для чего можно потребоваться ручная установка частоты ОЗУ?

Данное действие может потребоваться, например, в рамках мероприятий по разгону оперативной памяти. Большая частота оперативной памяти обычно позволяет обеспечить ее повышенную производительность, что, в свою очередь, может положительно влиять и на производительность всего компьютера. Однако следует помнить, что для того, чтобы добиться стабильной работы оперативной памяти, наряду с ее частотой может потребоваться одновременно настроить и другие параметры модулей ОЗУ, такие, как напряжение и тайминги.

Параметры частоты оперативной памяти компьютера можно настроить лишь при помощи соответствующих опций BIOS. Нужно иметь в виду, однако, что далеко не все системные платы позволяют изменить данный параметр оперативной памяти. Если в вашем распоряжении оказался компьютер с подобной материнской платой, то вы не сможете выставить нужную вам частоту, а в качестве ее значения будет использоваться номинальная величина для модуля ОЗУ.

Способ второй: AMI BIOS

Как можно понять, решать, какая оперативная память лучше, не стоит, ведь ее показатели можно легко изменить в настройках БИОС. Перейдем теперь к AMI BIOS и расскажем, как это сделать в нем.

- Войдя в CMOS, перейдите в меню «Advanced BIOS Features».

- В нем вам нужно отыскать строку «Advance DRAM Configuration» и нажать на ней Enter.

- Здесь находятся все те параметры, что были представлены в первом способе, то есть: подаваемое напряжение, тайминги и тактовая частота оперативной памяти.

По аналогии с Award BIOS, измените все параметры на нужные вам, сохраните их и перезапустите компьютер, чтобы войти в операционную систему.

Как узнать, какая оперативная память установлена в компьютере

Определить основные параметры оперативной памяти, установленной в компьютере, можно десятками способов. Все их мы рассматривать не будем, и приведем ниже наиболее удобные и простые варианты для рядового пользователя.

Видеоинструкция

Визуальный осмотр

Самый простой способ узнать основные параметры установленной в компьютере оперативной памяти – это осмотреть модуль уже установленного ОЗУ. Для этого предварительно необходимо отключить питание компьютера, после чего снять крышку и вытащить планку (для ее извлечения потребуется ослабить зажимы с обеих сторон). На ней должна быть наклейка с ключевой информацией об ОЗУ.

Плюсы визуального осмотра:

- Не требуется включать компьютер и загружать сторонние приложения;

- Помимо основных параметров оперативной памяти можно узнать точную ее модель.

Минусы визуального осмотра:

- Если наклейка с оперативной памяти была оторвана, информацию узнать не получится;

- На некоторые современные модули оперативной памяти не клеят наклейки с информацией из-за наличия на них радиатора охлаждения;

- Данный способ не подойдет для ноутбуков, поскольку снятие крышки с них является весьма трудоемкой процедурой.

Средствами BIOS

Через среду BIOS или UEFI можно определить основные параметры оперативной памяти, установленной в компьютере. Для этого нужно до начала загрузки операционной системы, то есть сразу после включения компьютера, нажимать Del, чтобы перейти в настройки BIOS. Далее действовать придется в зависимости от версии BIOS или UEFI:

- Если речь идет о старых версиях BIOS, искать информацию об оперативной памяти нужно в графе Memory Information, которая располагается во вкладке Chipset. Обратите внимание: в различных версиях BIOS место расположения информации об оперативной памяти может отличаться.

- Если речь идет о современном BIOS, то есть о UEFI, то искать информацию об оперативной памяти нужно на главном экране. В графе Total Memory указывается частота, тип и объем оперативной памяти, установленной в компьютере.

Плюсы определения параметров оперативной памяти средствами BIOS:

- Получить данные можно даже в том случае, если Windows на компьютере не установлен или не грузится;

- Если требуется проверять несколько модулей оперативной памяти подряд на определение их системой, данный способ наиболее быстрый.

Минусы получения сведений об оперативной памяти средствами BIOS:

- Поскольку версий BIOS много, и чаще всего они не локализованы, бывает трудно найти среди массы параметров информацию об оперативной памяти;

- В старом BIOS не всегда отображаются все необходимые сведения, и зачастую виден только объем оперативной памяти.

Средствами Windows

Операционная система Windows имеет встроенные утилиты, которые позволяют узнать минимальную информацию об оперативной памяти – ее используемый объем. То есть, определить утилитами операционной системы тип памяти и частоту не получится.

Имеется еще одно важное ограничение. Windows покажет только объем используемой памяти, а не суммарный размер установленной. На этот аспект следует обратить внимание, если на компьютере используется 32-разрядный Windows, который не поддерживает более 3 Гб оперативной памяти. То есть, если в компьютере установлено больше ОЗУ, это не будет отображаться в диагностических утилитах, и «лишняя» память не будет использоваться при работе.

Узнать объем оперативной памяти средствами Windows можно несколькими способами. Наиболее просто это сделать следующим образом:

- Нажать правой кнопкой мыши на значок «Мой компьютер» в проводнике и выбрать «Свойства». Откроется окно, где будет обозначен объем установленной оперативной памяти;

- Нажать на клавиатуре сочетание клавиш Windows+R и ввести команду msinfo32, после чего нажать Enter. Откроется окно «Сведения о системе», где информация об оперативной памяти хранится в основной вкладке.

Сторонними приложениями

Для Windows выпущена масса диагностических приложений, каждая из которых может быть использована для решения определенных задач. В большинстве из них предусмотрена возможность узнать информацию об оперативной памяти. Приведем ниже примеры подобных программ, которые можно бесплатно загрузить с сайтов разработчиков для определения сведений об оперативной памяти.

CPU-Z

Информация об оперативной памяти в приложении CPU-Z рассредоточена по нескольким вкладкам:

- Memory. В графе «General» значение «Type» расскажет о типе установленной оперативной памяти, а в пункте «Size» находится информация об объеме ОЗУ. Также ниже в графе «Timing» можно увидеть сведения о рабочей частоте.

- SPD. Во вкладке SPD можно определить количество установленных модулей памяти и подробную информацию о каждом из них.

AIDA64

Еще одним удобным приложением для просмотра информации об установленных в компьютере компонентах является AIDA64. Чтобы через программу узнать сведения об оперативной памяти, нужно во вкладке «Системная плата» выбрать пункт SPD. Приложение определяет все основные параметры ОЗУ.

HWiNFO64-32

HWiNFO64-32 – еще одно удобное приложение, которое позволяет диагностировать систему и проверять ее параметры. В отличие от AIDA64, данное приложение имеет portable-версию, то есть которую не требуется даже устанавливать на компьютер. Вся информация об оперативной памяти в приложении HWiNFO64-32 отображается в графе «Memory».

(10 голос., средний: 4,30 из 5)

-

Почему компьютер не видит жесткий диск

-

Как установить видеокарту

Похожие записи

Способ третий: UEFI BIOS

Теперь же перейдем непосредственно к настройке оперативной памяти в UEFI BIOS, пожалуй, самой удобной БИОС из всех. Так это, потому что она имеет графический интерфейс и поддерживает мышку, что значительно упрощает выполнения всех действий.

- Войдя в БИОС, вы должны перейти в расширенный режим. Для этого нажмите F7.

- Здесь перейдите на вкладку «Ai Tweaker».

- Найдите кнопку «Memory Frequency» и в выпадающем списке, который появится после нажатия по ней, выберите желаемую тактовую частоту.

- Чтобы настроить тайминги, вам необходимо перейти в меню «DRAM Timing Control».

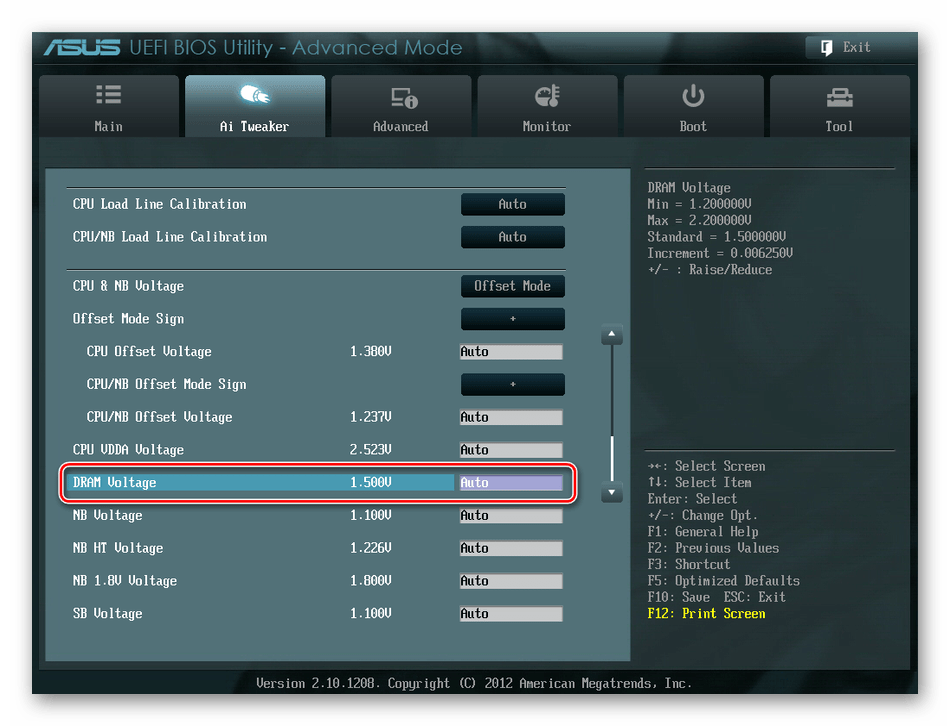

- Если вы решили поменять вольтаж, подаваемый на компонент, то вам необходимо перейти в меню «DRAM Voltage». Здесь, в соответствующем поле для ввода, укажите желаемый параметр.

Остается лишь сохранить все настройки и перезапустить компьютер – настройку оперативной памяти в UEFI BIOS можно считать оконченной.

Настройка BIOS. Оптимизация работы процессора

CPU Level 1 Cache – обязательно включите этот параметр. Он отвечает за использование кэша первого уровня, значительно повышает работоспособность всей системы.

CPU Level 2 Cache – этот параметр играет не менее важную роль, чем предыдущий. Поэтому включаем его. Для справки: отключение кеш-памяти можно производить только при выходе ее из строя, но это значительно снизит производительность системы в целом.

CPU Level 2 Cache ECC Check – параметр включения/выключения алгоритма проверки коррекции ошибок в кеш-памяти 2-го уровня. Включение этого параметра незначительно снижает производительность, но повышает стабильность работы. Если вы не занимаетесь разгоном процессора, советую вам не включать этот параметр.

Boot Up System Speed – параметр имеет значение High либо Low и определяет скорость процессора и частоту системной шины. Наш выбор – High.

Cache Timing Control – параметр управляет скоростью чтения памяти кеш 2-го уровня. Наш выбор – Fast (Turbo) – высокая скорость, высокая производительность.

Как изменить частоту оперативной памяти | Сделай все сам

1. Увеличить частоту оперативной памяти дозволено двумя методами: изменить ее множитель либо частоту системной шины. Класснее применять 2-й вариант, так как он обеспечивает плавный приход продуктивности, а не крутой скачек, тот, что может привести к порче устройства. Установите утилиту Speccy и запустите ее. Откройте меню «Оперативная память» и посмотрите частоту , с которой работают платы в данный момент.

2. Перезагрузите компьютер и откройте BIOS, нажав клавишу Del. Откройте меню Advanced и обнаружьте пункт FSB/Memory Ratio. Он может именоваться напротив в разных моделях материнских плат. Установите для этого пункта параметр Manual взамен Auto. Сейчас вы можете самосильно задать значения частоты и множителя. Исполните эти действия. Увеличьте частоту шины оперативной памяти на 20-50 Герц.

3. Вернитесь в основное окно меню BIOS и выберите пункт Save & Exit. Нажмите клавишу Enter и дождитесь перезагрузки компьютера. Сейчас исполните проверку устойчивости оперативной памяти .

Откройте панель управления и выберите меню «Система и безопасность» (Windows Seven). Откройте подменю «Администрирование» и запустите ярлык «Проверка памяти Windows».

Удостоверите выполнение перезагрузки компьютера для проверки состояния оперативной памяти .

4. Если тестирование показало отличные итоги, то повторите вход в меню BIOS и опять поднимите частоту оперативной памяти . Исполняйте описанные циклы до тех пор, пока система проверки ОЗУ не выявит ошибок. Позже этого можете испробовать уменьшить задержки памяти . Для этого поочередно понижайте на один пункт показатели четырех видов таймингов. Традиционно они расположены в Advanced Settings.

5. Если во время метаморфозы параметров работы ОЗУ случился сбой, а компьютер перестал загружаться, то извлеките на некоторое время BOIS-батарейку из системного блока. Это дозволит применить заводские настройки ПК.

Совет 2: Как выставить частоту памяти

Для полной оптимизации компьютера нужно настроить параметры работы плат оперативной памяти . Данный процесс рекомендуют исполнять через меню BIOS, но изредка дозволено применять добавочные программы.

Совет 3: Как увеличить частоту оперативной памяти

Каким бы стремительным не был ваш компьютер либо ноутбук, со временем его мощности перестает хватать и он огромнее не может справляться с надобными вам задачами. Тогда и появляется мысль о разгоне его компонентов. Касательно порядочного увеличения продуктивности дозволено добиться, разгоняя оперативную память компьютера. Только помните, что разгон приводит к уменьшению устойчивости работы компьютера, следственно его нужно проводить с осторожностью и только при острой необходимости.

Вам понадобится

Совет 4: Как изменить тайминг памяти

Если вам требуется повысить продуктивность оперативной памяти, не прибегая к установке новых планок ОЗУ, то уменьшите тайминги существующих. Делать это следует весьма старательно, чтобы не повредить устройства компьютера.

Вам понадобится

Установка, настройка и разгон оперативной памяти

Не все знают, что оперативную память недостаточно просто установить в компьютер. Её полезно настроить, разогнать. Иначе она будет давать минимально заложенную в параметры эффективность. Здесь важно учесть, сколько планок установить, каким образом распределять их по слотам, как проставить параметры в БИОСе. Ниже вы найдёте советы по установке RAM, узнаете, как правильно установить, настроить и разогнать оперативную память.

Узнайте, как правильно установить, настроить и разогнать оперативную память самому

Совмещение разных модулей

Первый вопрос, возникающий при желании повысить производительность, быстродействие ОЗУ у пользователей, — возможно ли установить в компьютер модули памяти разного производства, отличающиеся частотой? Решая, как установить оперативную память в компьютер, приобретайте лучше модули одного производства, с одной частотностью.

Теоретически, если установить модули разночастотные, оперативная память работает, но на характеристиках самого медленного модуля. Практика же показывает, что зачастую возникают проблемы несовместимости: не включается ПК, происходят сбои ОС.

Следовательно, при планах установить несколько планок покупайте набор в 2 либо 4 модуля. В одинаковых планках чипы обладают одинаковыми параметрами разгонного потенциала.

Полезность многоканального режима

Современный компьютер поддерживает многоканальность в работе оперативной памяти, минимально оборудованы 2 канала. Есть процессорные платформы с трёхканальным режимом, есть с восемью слотами памяти для четырёхканального режима.

При включении двухканального режима прибавляется 5–10% производительности процессору, графическому же ускорителю — до 50%. Потому при сборке даже недорогого игрового устройства рекомендуется установка минимум двух модулей памяти.

Настройка оперативной памяти в BIOS

Видео инструкция

Настраиваем RAM в BIOS

Изменять можно основные характеристики оперативной памяти, то есть тактовую частоту, тайминги и напряжение. Все эти показатели взаимосвязаны. И поэтому к настройке оперативной памяти в БИОС нужно подходить теоретически подготовленным.

Способ 1: Award BIOS

Если на вашей системной плате установлена прошивка от Phoenix/Award, то алгоритм действий будет выглядеть примерно так, как указано ниже. Помните, что названия параметров могут незначительно отличаться.

- Делаем перезагрузку ПК. Входим в БИОС с помощью сервисной клавиши или сочетания клавиш. Они бывают различные в зависимости от модели и версии «железа»: Del, Esc, F2 и так далее.

- Нажимаем комбинацию Ctrl + F1 для входа в расширенные настройки. На открывшейся странице стрелками переходим в пункт «MB Intelligent Tweaker (M.I.T.)» и нажимаем Enter.

В следующем меню находим параметр «System Memory Multiplier». Изменяя его множитель, можно уменьшать или увеличивать тактовую частоту работы оперативной памяти. Выбираем чуть больше действующей.

Можно осторожно увеличить напряжение тока, подаваемого на RAM, но не более чем на 0,15 вольта.

Здесь можно настроить тайминги, то есть время отклика устройства. В идеале, чем меньше этот показатель, тем быстрее функционирует оперативная память ПК. Сначала меняем значение «DRAM Timing Selectable» с «Auto» на «Manual», то есть на режим ручной регулировки. Затем можно поэкспериментировать уменьшая тайминги, но не более чем на единицу единовременно.

Настройки закончены. Выходим из BIOS с сохранением изменений и запускаем любой специальный тест для проверки стабильности работы системы и RAM, например, в AIDA64.

Способ 2: AMI BIOS

Если БИОС на вашем компьютере от American Megatrends, то кардинально значительных отличий от Award не будет. Но на всякий случай вкратце рассмотрим этот случай.

Далее переходим в «Advance DRAM Configuration» и производим необходимые изменения тактовой частоты, напряжения и таймингов оперативной памяти по аналогии со Способом 1.

Способ 3: UEFI BIOS

На большинстве современных материнских плат стоит UEFI BIOS с красивым и удобным интерфейсом, поддержкой русского языка и компьютерной мыши. Возможности по настройке RAM в такой прошивке очень широкие. Рассмотрим их подробно.

- Заходим в БИОС, нажав Del или F2. Реже встречаются другие сервисные клавиши, узнать их можно в документации или из подсказки внизу экрана. Далее переходим в «Advanced Mode», нажав F7.

На странице расширенных настроек переходим на вкладку «Ai Tweaker», находим параметр «Memory Frequency» и в выпадающем окне выбираем желаемую тактовую частоту оперативной памяти.

Продвигаясь ниже по меню, видим строку «DRAM Timing Control» и нажав на нее, попадаем в раздел регулировки различных таймингов RAM. ПО умолчанию во всех полях стоит «Auto», но при желании можно попробовать поставить свои значения времени отклика.

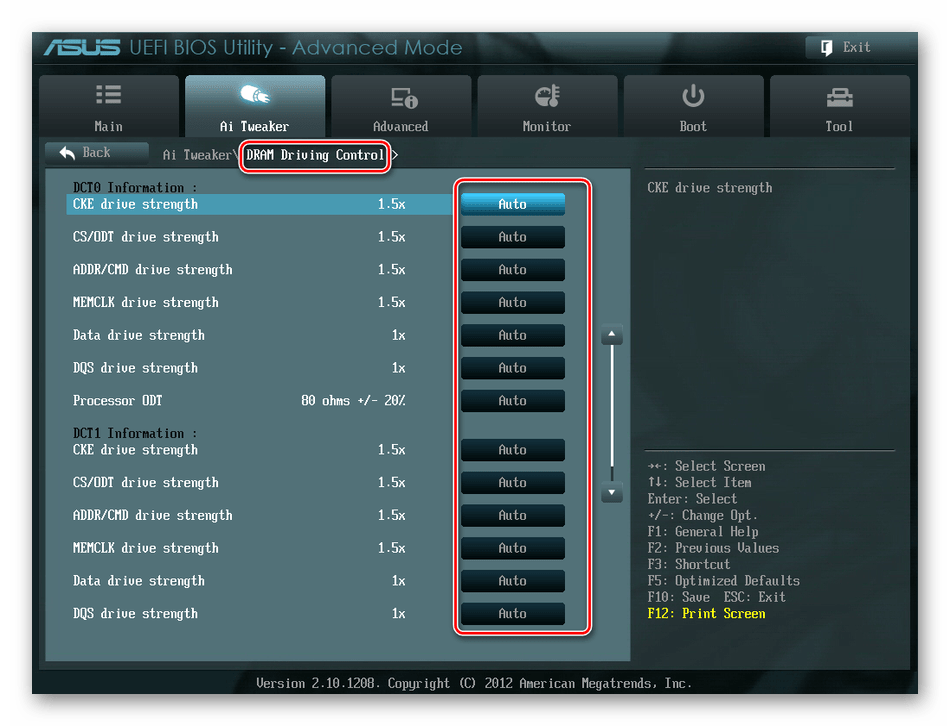

Возвращаемся в меню «Ai Tweaker» и заходим в «DRAM Driving Control». Здесь можно попытаться чуть увеличить множители частоты RAM и ускорить её работу. Но делать это надо осознанно и осторожно.

Опять возвращаемся на прошлую вкладку и далее наблюдаем параметр «DRAM Voltage», где можно изменять подаваемое на модули оперативной памяти напряжение электрического тока. Повышать вольтаж можно на минимальные значения и поэтапно.

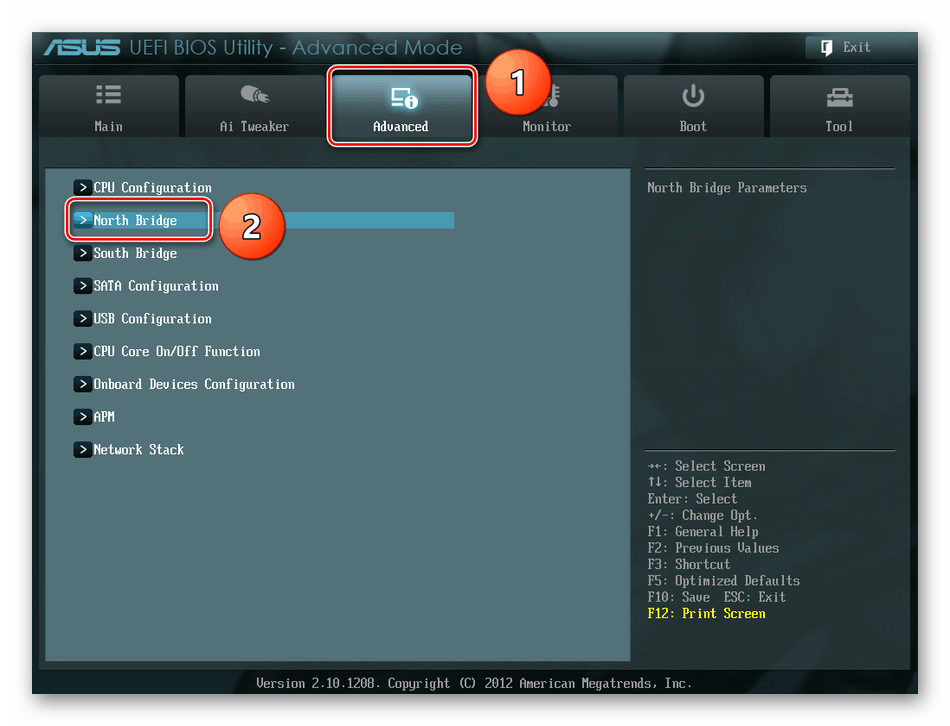

Затем выходим в окно расширенных настроек и передвигаемся во вкладку «Advanced». Там посещаем «North Bridge», страницу северного моста материнской платы.

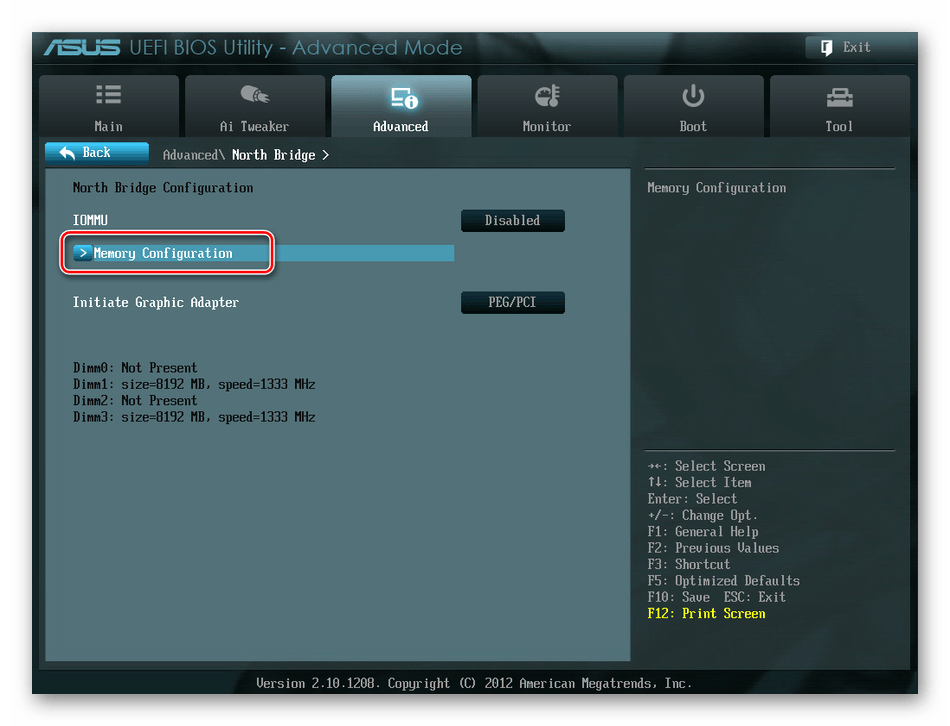

Здесь нас интересует строка «Memory Configuration», на которую и нажимаем.

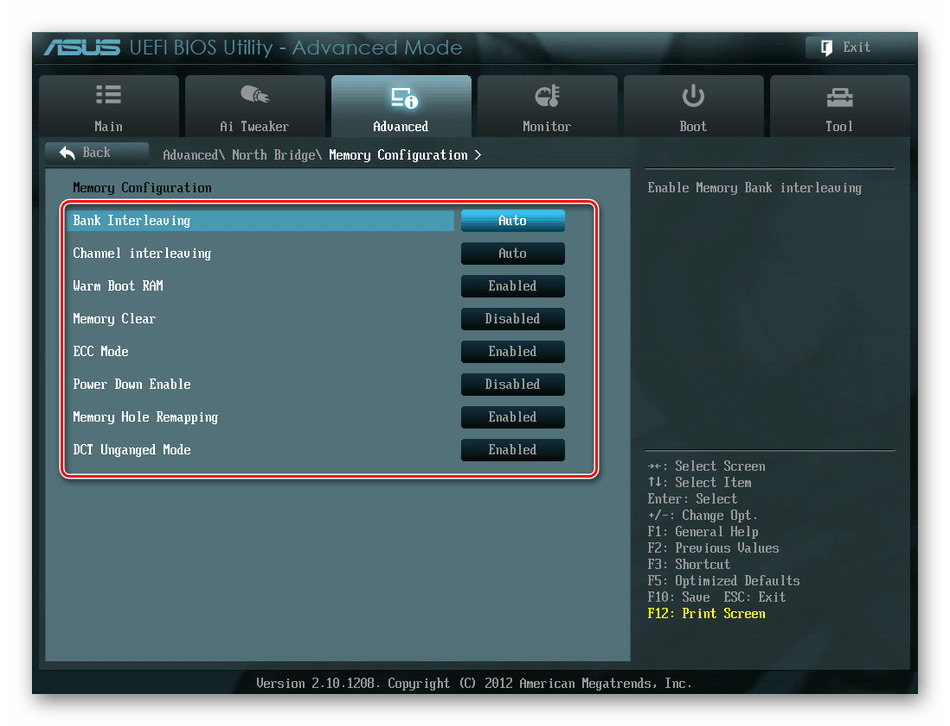

В следующем окне можно изменить параметры конфигурации модулей оперативной памяти, установленных в ПК. Например, включить или выключить контроль и коррекцию ошибок (ECC) RAM, определить режим чередования банков оперативной памяти и так далее.

Как вы увидели, настройка оперативной памяти в БИОС вполне возможна для опытного пользователя. В принципе, в случае ваших некорректных действий на этом направлении компьютер просто не включится или прошивка сама сбросит ошибочные значения. Но осторожность и чувство меры не помешает. И помните, что износ модулей RAM при увеличенных показателях соответственно ускоряется.

Источник

Установка частоты модулей RAM в BIOS

Видео инструкция

Выбор частоты ОЗУ

Прежде, чем приступить к увеличению частоты памяти, отметим несколько важных моментов.

- Далеко не все материнские платы поддерживают такую функцию: чаще всего настройка частоты попадается в моделях, нацеленных на геймеров или компьютерных энтузиастов. Также подобные настройки обычно отсутствуют в ноутбуках.

- Обязательно нужно учитывать тип установленной RAM, особенно в БИОСах, где есть возможность вручную прописать значение частоты.

- Повышенные частоты обычно сопровождаются и повышением выделяемого тепла, поэтому строго рекомендуется установить серьёзное охлаждение.

Собственно процедура увеличения memory frequency отличается от типа BIOS, установленного на плату.

Внимание! Для полноценного разгона оперативной памяти просто увеличить частоту недостаточно – потребуется также изменить некоторые другие параметры вроде таймингов и вольтажа! Об этом рассказано в отдельном материале!

Рассмотрим на примерах наиболее распространённых вариантов. Разумеется, сперва в БИОС нужно зайти – в статье по ссылке ниже вы найдёте детальное руководство по входу в интерфейс микропрограммы.

Текстовый вариант

Классические текстовые БИОС с управлением с клавиатуры уходят в прошлое, но для некоторых пользователей всё ещё актуальны.

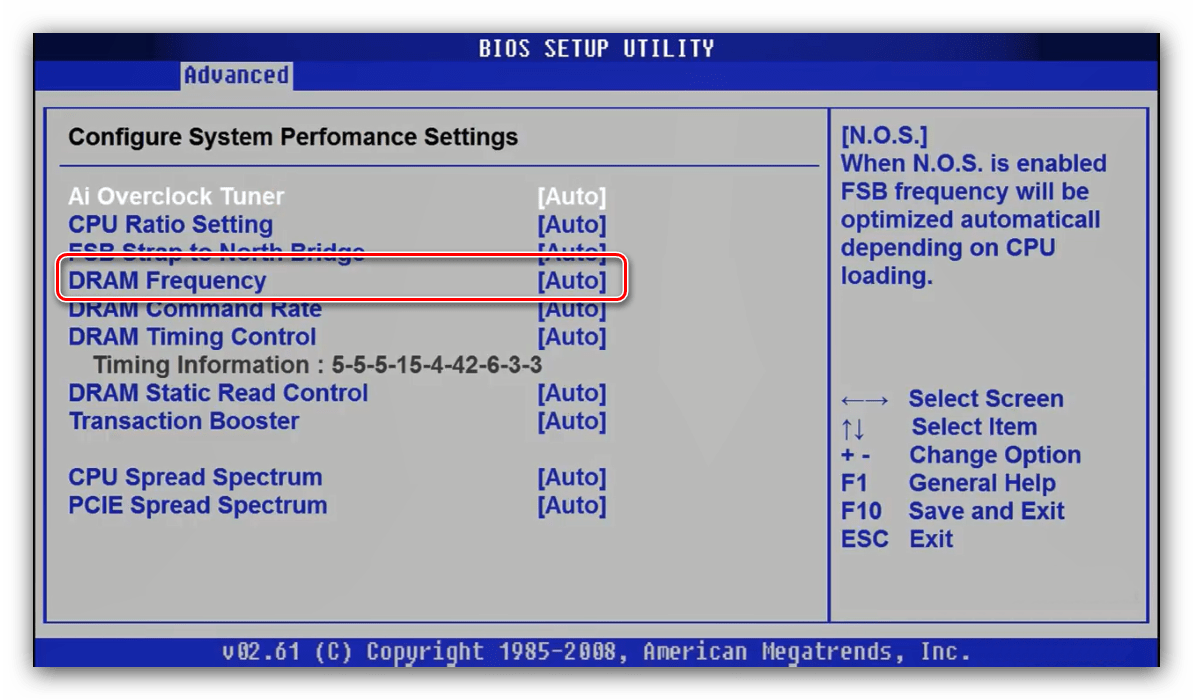

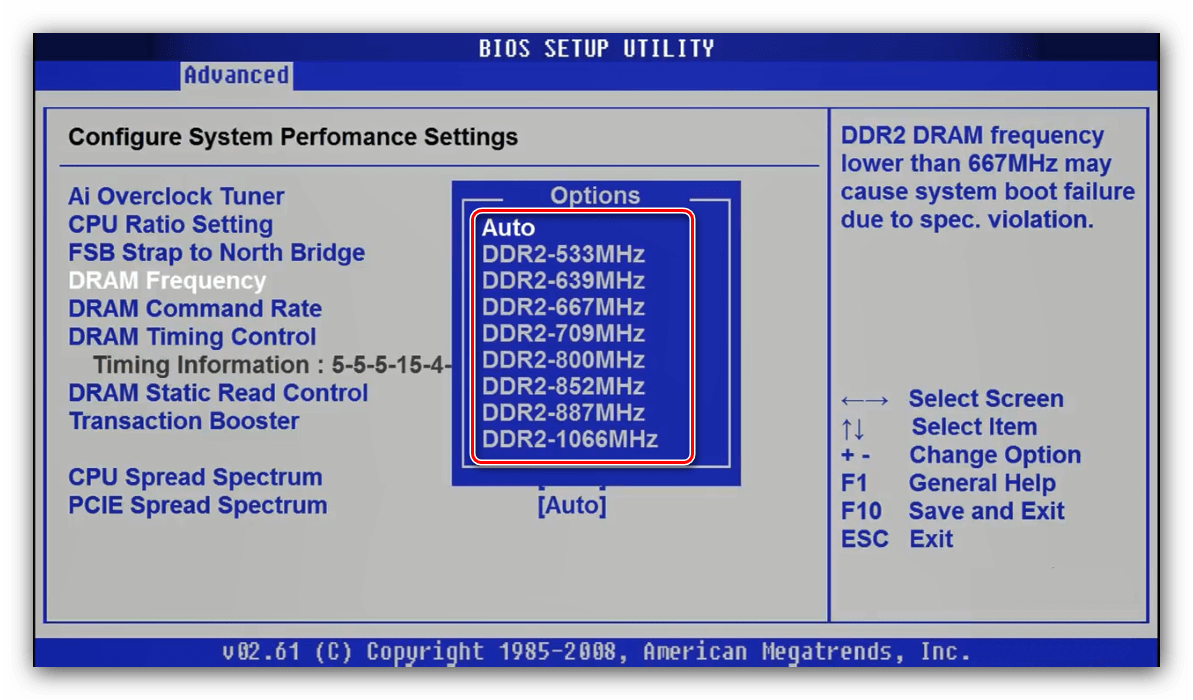

- Войдите в интерфейс прошивки и перейдите на вкладку «Advanced».

Воспользуйтесь опцией «DRAM Frequency» – выберите её стрелочками и нажмите Enter.

В некоторых вариантах этого интерфейса данная опция находится внутри подменю «JumperFree Configuration».

Выберите во всплывающем меню подходящую частоту. Обратите внимание, что для удобства приведены как числовые значения в МГц, так и соответствующие им типы памяти. Снова используйте стрелки и Enter.

Award

- В главном меню BIOS воспользуйтесь опцией «MB Intelligent Tweaker».

Для настройки частоты памяти первым делом переключите параметр «Set Memory Clock» в положение «Manual».

Далее воспользуйтесь настройкой «Memory Clock». В Award BIOS изменение частоты достигается за счёт выбора множителя. Если вам сложно ориентироваться в них, можете выставить любой и проверить значение в мегагерцах рядом с опцией. Пропорция очень простая – чем выше множитель, тем более высокая частота получается.

Phoenix

- В главном меню выберите вариант «Frequency/Voltage Control».

Далее воспользуйтесь меню «Memory Feature».

Найдите опцию «Memory Control Setting», её нужно установить в положение «Enable». Далее откройте меню «Memory Frequency» – установите желаемую частоту с помощью стрелок и клавиши Enter.

Обращаем ваше внимание – в некоторых случаях опции в каждом из рассматриваемых БИОС могут менять название или местоположение – зависит от производителя материнской платы.

Графическая оболочка

Практически все современные продвинутые платы идут с графическим UEFI-интерфейсом, более удобным в освоении. Следовательно, настройка тактовой частоты RAM в подобных вариантах микропрограммы достаточно простая.

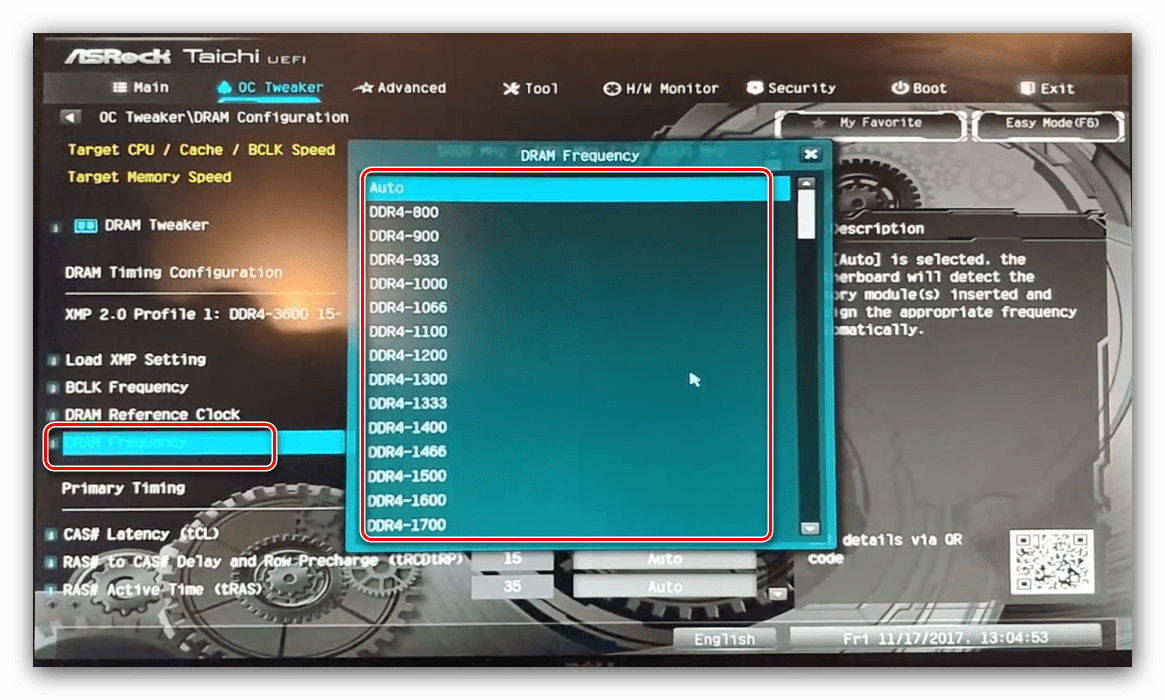

ASRock

- Перейдите в Advanced Mode нажатием на клавишу F6.

- Откройте закладку «OC Tweaker», где воспользуйтесь меню «DRAM Configuration».

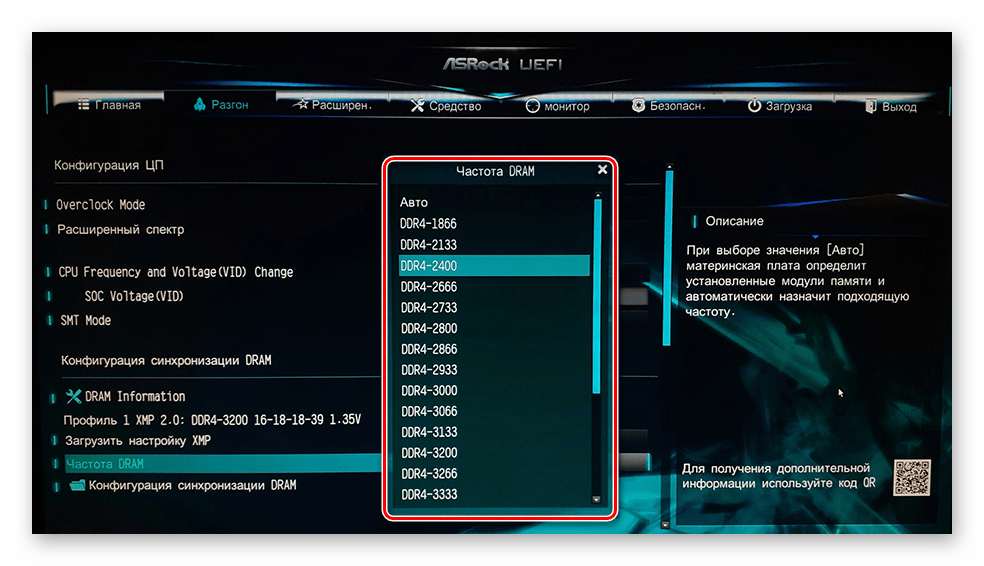

Зайдите в меню «DRAM Frequency» – появится список с доступными частотами, соответствующими типу ОЗУ. Выберите подходящий.

ASUS

- После загрузки БИОСа нажмите клавишу F7 для перехода в продвинутый режим.

В продвинутом режиме перейдите ко вкладке «AI Tweaker» (в некоторых вариантах плат называется «Extreme Tweaker»). Первым делом установите опцию «AI Overclock Tuner» в положение «D.O.C.P.».

Далее воспользуйтесь опцией «Memory Frequency». Появится всплывающее меню, в котором выберите подходящее значение для вашего типа оперативной памяти.

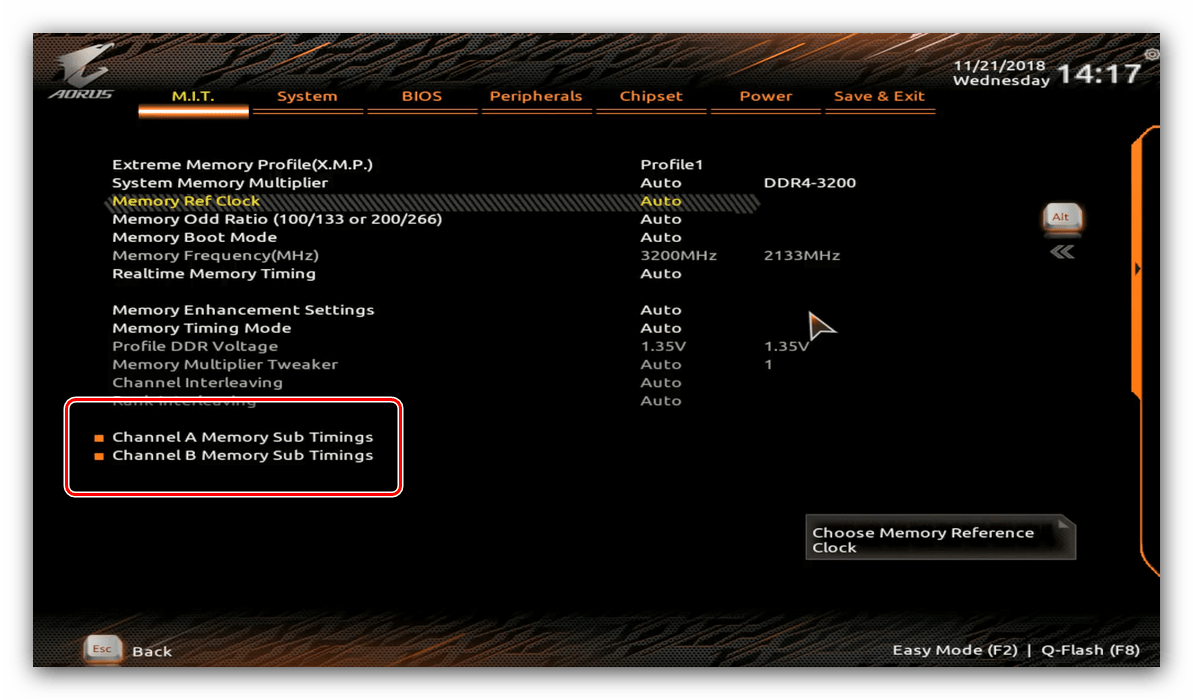

Gigabyte

- В главном меню БИОС нажмите клавишу F2 для перехода в продвинутый режим. Откройте вкладку «M.I.T».

Откройте меню «Advanced Memory Settings».

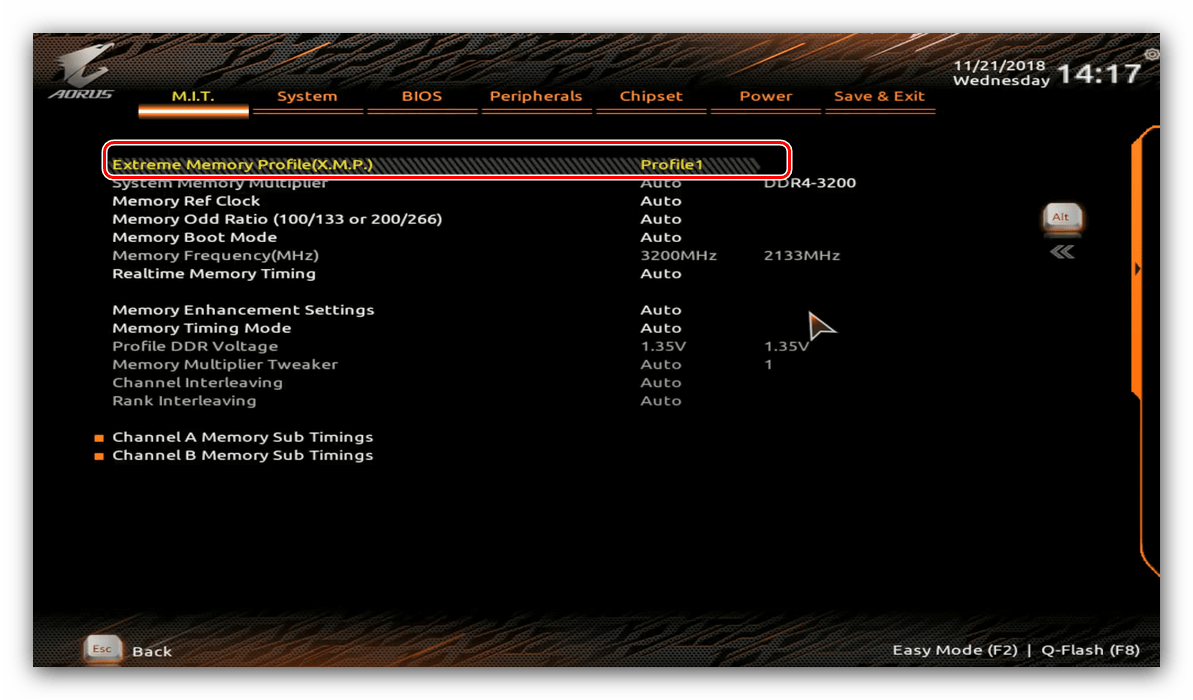

В «Extended Memory Profile» выберите новый профиль, должен появится «Profile 1».

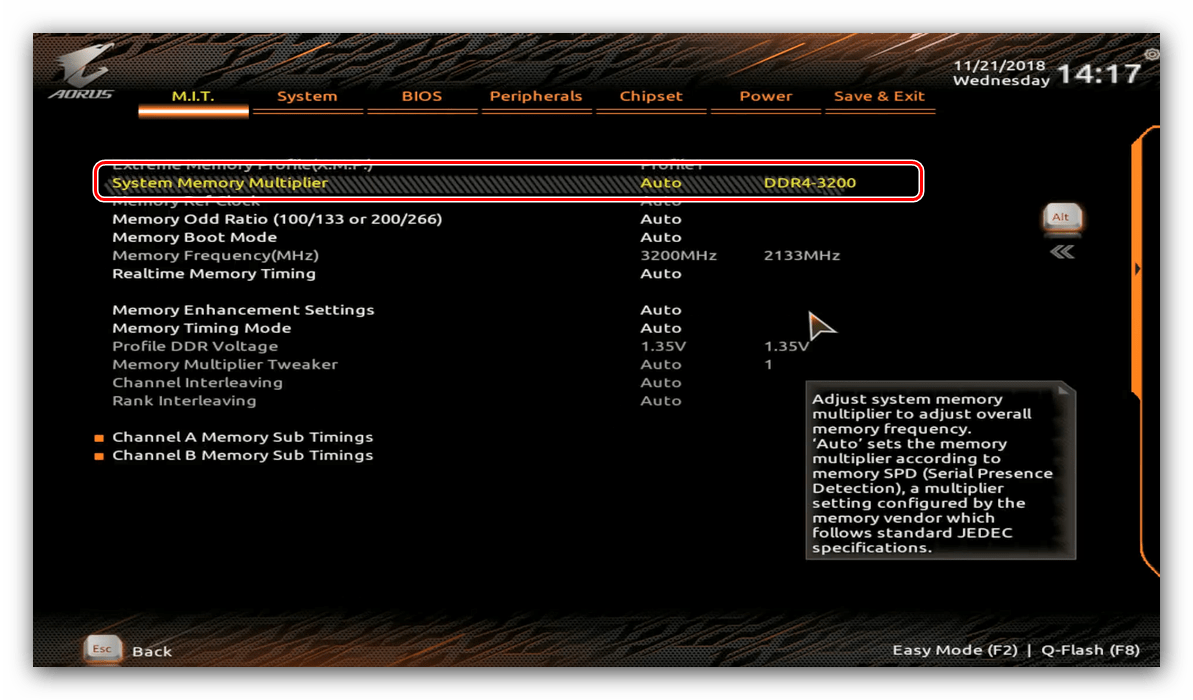

Далее воспользуйтесь настройкой «System Memory Multiplier». Выберите в ней вариант, который соответствует конкретно вашему типу ОЗУ.

Остальные опции можно оставить по умолчанию, однако по желанию можно открыть меню «Channel Memory Subtimings» вручную прописать тайминги для каждого из используемых каналов.

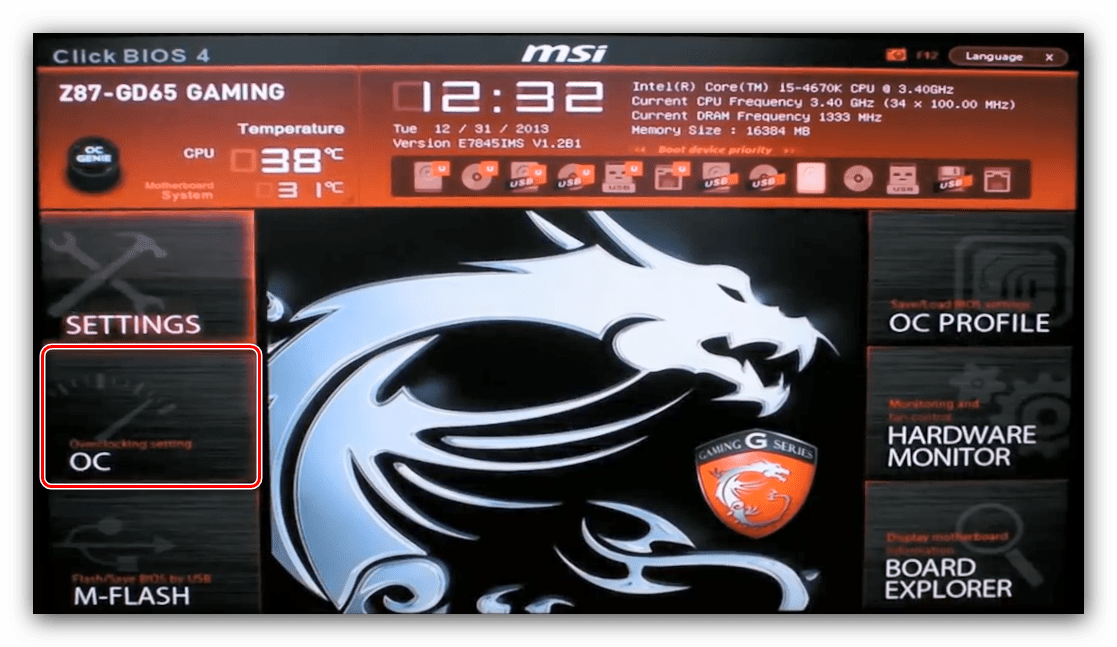

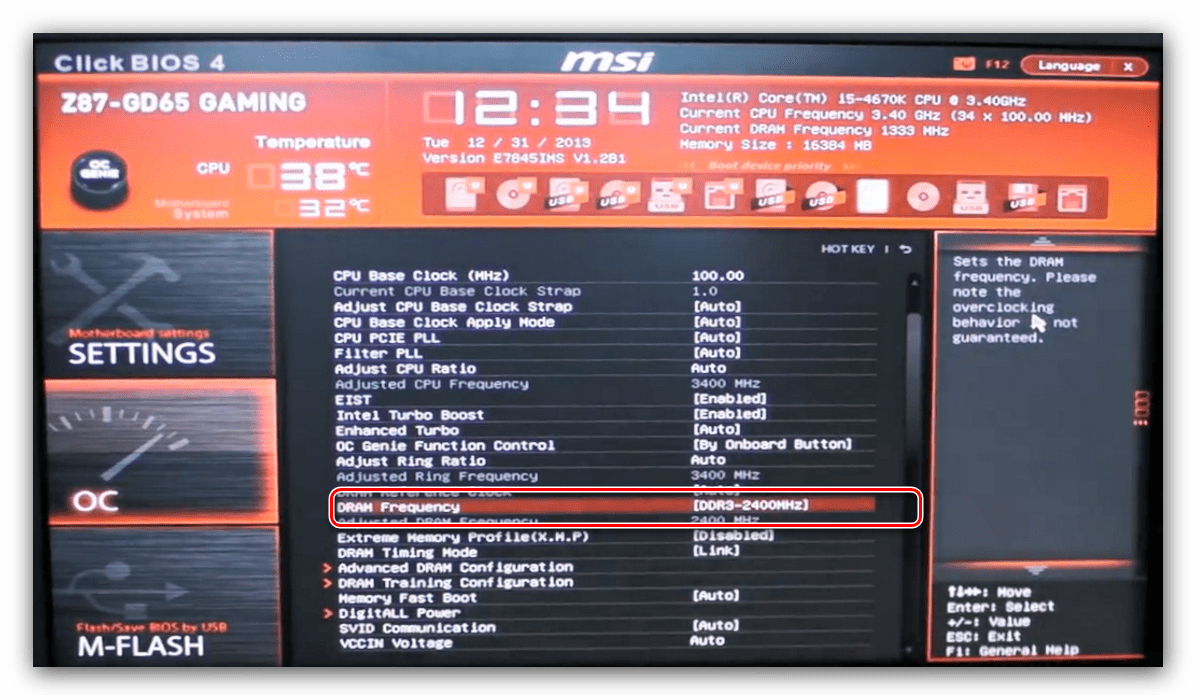

- Воспользуйтесь кнопкой F7, чтобы открыть расширенный режим настроек. Используйте пункт меню «OC».

Читайте также: Настройка BIOS на MSI

Используйте пункт «DRAM Frequency». Выберите нужную частоту во всплывающем меню.

Заключение

На этом заканчиваем описание методов настройки частоты оперативной памяти через разнообразные BIOS. Напоследок ещё раз напоминаем – изменять эти параметры следует только в том случае, когда вы хорошо понимаете, что делаете.

Источник

Вход в БИОС

Во многих версиях БИОС есть настройки оперативной памяти. Способ входа в него может отличаться в зависимости от материнской платы. Клавиша, на которую необходимо нажать, чтобы войти в БИОС, указывается в нижнем углу в начале загрузки компьютера.

На большинстве современных материнских плат используется UEFI. В них настройки оперативной памяти находятся на вкладке «Разгон». В старых версиях БИОС их можно найти, перейдя в расширенные настройки с помощью сочетания клавиш Ctrl+F1 и открыв вкладку «MB Intelligent Tweaker (M.I.T.)».

Способ 1: Настройка через XMP

На старых материнских платах этот способ может не работать

Иногда бывает, что ОЗУ запускается на характеристиках, отличающихся от указанных на сайте производителя. Тогда нужно проверить, есть ли в оперативной памяти установленный XMP, в котором будут сразу выставлены подобранные значения частоты, таймингов и напряжения.

- Найдите пункт «Загрузить настройку XMP» и зайдите в него.

- В появившемся окне нажмите на подходящий профиль. Характеристики каждого из них можно посмотреть на вкладке «DRAM Information». Для гарантии стабильной работы нужно выбирать вариант, отталкиваясь от характеристик материнской платы и процессора (информация о максимальной поддерживаемой частоте есть на сайте производителя). Если характеристики XMP выше поддерживаемых, то его все равно можно выбрать, главное, чтобы компьютер при этом продолжал правильно работать даже под нагрузкой (игры, программы), не вылетая в синий экран. В противном случае, нужно выбрать менее требовательный вариант, если он есть, либо настроить оперативную память вручную.

Способ 2: Ручная настройка

Если подходящий XMP отсутствует, настраивать ОЗУ нужно вручную. Делается это на той же вкладке «Разгон».

- Обычно сначала выбирается частота, на которой будет работать память. Сделать это можно в пункте «Частота DRAM». В некоторых версиях частота выбирается через «System Memory Multiplier», путем изменения ее множителя.

- В появившемся списке частот нажмите на подходящую под характеристики компьютера. Можете попробовать поставить значение выше, тем самым разогнав ОЗУ, но память при этом может не запуститься (особенно, если она бюджетная). Если это произошло, просто верните старое значение, и ОЗУ снова заработает.

- После определения частоты требуется подобрать тайминги. Чем они меньше, тем лучше, но при этом с увеличением частоты тайминги тоже должны увеличиваться. Настроить их можно, перейдя в «Конфигурацию синхронизации DRAM». В старых БИОС тайминги меняются в меню с расширенными настройками, в пункте «Advanced Chipset Features».

- Слева написаны значения, на которых ОЗУ работает в данный момент, справа — выбранные пользователем, которые вступят в силу после выхода из БИОСа. Определенного алгоритма по подбору таймингов нет, нужно путем экспериментов изменять каждое значение (не больше, чем на 1 за раз) и замерять быстродействие оперативной памяти с помощью программ для мониторинга. Чтобы было проще, можно найти в интернете готовые наборы значений и отталкиваться уже от них.

- После повышения быстродействия памяти следует увеличить ее рабочее напряжение, чтобы она стабильно работала под нагрузками — за это отвечает опция «Напряжение DRAM» («Voltage Control»). Как и в случае с таймингами, слева указано то значение, на котором ОЗУ работает в данный момент, справа — выбранное пользователем.

- Когда все настройки будут подобраны, перейдите на вкладку «Выход» («Exit») и выберите вариант с сохранением внесенных изменений. Если после этого компьютер стал работать быстрее, значит ОЗУ настроена правильно.

Не изменяйте это значение больше, чем на 0.15 вольт за раз!

Пожалуй, наиглавнейшим моментом в вопросе четкого функционирования компьютера является настройка параметров различных подсистем из BIOS Setup, мимо которой пройти просто невозможно. Основная система ввода/вывода (BIOS — Basic Input Output System) является своего рода “прослойкой” между аппаратной (комплектующие) и программной (операционная система) частями ПК. В ней содержится информация относительно установленных компонент и общих настроек всей системы. Однако большинство установок имеют свою специфику, определяя некоторые особенности и тонкости функционирования управляемых ими подсистем. Систему можно настроить на максимальную эффективность, установив соответствующие параметры на максимально возможные значения с точки зрения производительности, но при этом нет никакой гарантии, что компьютер будет работать надежно и без сбоев. С другой стороны, систему можно настроить на максимальную отказоустойчивость, “загрубив” при этом производительность. Каждая из этих крайностей имеет свои плюсы и минусы, поэтому обычно стремятся достичь “золотой середины”, варьируя значения соответствующих пунктов настройки BIOS Setup. Таким образом, можно получить оптимально сбалансированные параметры и добиться максимально возможной производительности при обеспечении стабильного функционирования ПК.

Основными моментами в данном вопросе являются установки параметров, предназначенных для конфигурирования системного ОЗУ (оперативной памяти): всевозможные задержки, специфические режимы работы, общие схемы функционирования и т.д. — все, что касается этого вопроса можно найти в разделе “Advanced Chipset Setup” (или “Chipset Features Setup”) в BIOS Setup.

Auto Configuration

Этот пункт в настройке является, пожалуй, основным, однако встречается не в каждой системе — точнее сказать, на всех материнских платах для 486-совместимых процессоров и на большей части Pentium-совместимых материнских плат. Он определяет возможность изменений в настройках подсистемы памяти типа FPM DRAM и EDO DRAM, указывая длительность цикла обращения (минимальный промежуток времени в течение которого можно выполнить циклическое обращение по произвольный адресам) к данным: 60ns (оптимизировано для микросхем памяти с временем доступа 60ns), 70ns (оптимизировано для микросхем памяти с циклом доступа 70ns) и Disable (в данном случае разрешить “ручную” настройку имеющихся параметров подсистемы памяти). При асинхронной передаче данных гарантируется, что определенная операция будет полностью осуществлена за фиксированный промежуток времени, поскольку в данном случае функционирование памяти не привязывается к частоте системной шины. Поэтому, если данные появляются сразу за фронтом системного синхросигнала, то они будут считаны лишь по приходу следующего фронта тактового импульса. Значения 60/70 ns данного пункта указывают системе, что надо использовать предустановки, занесенные производителем материнской платы заранее, которые обеспечивают стабильную работу памяти, исходя из установленной длительности цикла доступа. Понятно, что при этом наверняка теряется некоторая часть максимально возможной производительности. Поэтому, чтобы дать возможность проведения гибкой конфигурации, этот параметр необходимо установить в положение Disable, открыв доступ к другим установкам настройки подсистемы памяти.

DRAM Read Timing

Параметр, характеризующий скорость чтения данных из массива памяти. Сам массив представляет собой некое подобие координатной сетки, где есть положение по горизонтали (адрес строки) и по вертикали (адрес столбца). Упрощенно, на пересечении каждого конкретного адреса строки и столбца находится единичный “строительный элемент” массива — ячейка памяти, которая представляет собой ключ (транзистор) и запоминающий элемент (конденсатор). Логическое состояние ячейки (физически — заряд в конденсаторе) представляется довольно просто: есть заряд — “1”, нет заряда — “0”.

Для чтения содержимого из одной ячейки памяти в самом простом случае необходимо пять тактов. Сначала на шину выставляется адрес строки (первая половина полного адреса ячейки памяти). Затем подается строб RAS# (Row Address Srobe), который является своего рода контрольным сигналом (защелка адреса строки), подтверждающим полученный адрес строки для записи в специально отведенное место — регистр микросхемы памяти. После этого передается адрес столбца (вторая половина полного адреса ячейки памяти), следующим тактом за которым идет сигнал подтверждения принимаемого адреса (защелка адреса столбца) — CAS# (Column Address Strobe). И, наконец, следует операция чтения из ячейки памяти, контролируемая сигналом разрешения записи — WE# (Write Enable). Однако если считываются соседние ячейки, то нет надобности передавать каждый раз адрес строки или столбца, и процессор “считает”, что необходимые данные расположены по соседству. Поэтому на считывание каждой последующей ячейки понадобится уже три такта системной шины. Отсюда и берет свое начало существование определенных схем функционирования (тайминги, в широком смысле этого понятия, обычно означающего временной параметр) конкретного фундаментального типа ОЗУ: xyyy-yyyy-…, где x — количество тактов шины, необходимое для чтение первого бита, а у — для всех последующих.

Так, цикл доступа процессора к памяти состоит из двух фаз: запроса (Request) и ответа (Response). Фаза запроса состоит из трех действий: подача адреса, подача запроса на чтение и подтверждение (необязательно). В фазу ответа входит выдача запрашиваемых данных и подтверждение приема. Довольно часто происходит чтение четырех смежных (соседних) ячеек, поэтому многие типы памяти специально оптимизированы для данного режима работы, и в сравнительных характеристиках быстродействия обычно приводится только количество циклов, необходимое для чтения первых четырех ячеек. В данном случае речь идет о пакетной передаче, которая подразумевает подачу одного начального адреса и дальнейшую выборку по ячейкам в установленном порядке — такого рода трансфер улучшает скорость доступа к участкам памяти с заранее определенными последовательными адресами. Понятно, что в случае необходимости чтения данных с непоследовательного адреса в “цепочке” пакетной передачи возникает разрыв и первый бит следующего произвольного обращения (адреса) считается со стандартным пятитактным доступом, описаваемым выше. Обычно процессор формирует адресные пакеты на четыре передачи данных вперед, поскольку предполагается, что система автоматически возвратит данные из указанной ячейки и трех следующих за ней. Преимущество такой схемы очевидно: на передачу четырех порций данных требуется всего одна фаза запроса.

Например, для памяти типа FPM DRAM применяется схема 5333-3333-…, в отличие от первой разновидности динамического ОЗУ, где применялась самая простая — 5555-5555-… Для памяти EDO DRAM после первого считывания блока данных увеличивается время доступности данных того ряда, к которому происходит доступ в настоящий момент, при этом уменьшается время получения пакета данных, т.к. схема доступа уже 5222-2222-… Синхронное ДОЗУ типа SDRAM, в отличие от асинхронного (FPM и EDO), “свободно” от передачи в процессор сигнала подтверждения и выдает/принимает данные в строго определенные моменты времени (только совместно с сигналом синхронизации системной шины), что исключает несогласованность между отдельными компонентами, упрощает систему управления и дает возможность перейти на более “короткую” схему работы: 5111-1111-… Аналогичную временную диаграмму имеет и пакетное ДОЗУ на основе схемы расширенного доступа к данным (BEDO DRAM) — последняя разновидность асинхронного типа динамической памяти.

Поэтому в рассматриваемом пункте меню настройки можно встретить варианты допустимых значений для циклов обращения к памяти: x333 или x444 оптимально подходит для FPM DRAM, x222 или x333 — для EDO DRAM, и x111 или x222 — для BEDO DRAM (и SDRAM). Варьируя эти параметры и стараясь использовать более короткую диаграмму для конкретного типа памяти, можно добиться некоторого повышения производительности.

DRAM Write Timing

Параметр, аналогичный по принципу предыдущему, с той разницей, что происходит настройка произведения операций записи. Для фундаментальных типов памяти FPM DRAM и EDO DRAM значение рассматриваемого параметра одинаково, поскольку выигрыш от принципа EDO можно получить только на операциях чтения. Соответственно, устанавливаемые значения аналогичны “DRAM Read Timing”, принимая во внимание особенности архитектуры используемой памяти.

Fast RAS-to-CAS Delay

Установка, характеризующая задержку в циклах тактового сигнала между стробами RAS# и CAS# (как уже говорилось, по сигналам RAS# и CAS# внутрикристальные триггеры фиксируют части полного адреса — строки и столбца), за которую данные из накопителя ДОЗУ передаются на выходные усилители (SenseAmp, играющие роль временного буфера и усилителя уровня, поскольку сигнал, выходящий из микросхемы, достаточно слабый), и обычно составляющую 2ns. Эта задержка вводится умышленно и необходима для того, чтобы было достаточно времени для однозначного определения адреса строки (сигнал RAS#) и столбца (сигнал CAS#) ячейки. Иными словами, данный параметр характеризует интервал между выставлением на шину контроллером памяти сигналов RAS# и CAS#. Понятно, что чем меньше данное значение, тем лучше, однако не стоит забывать, что за ним стоит возможность самих микросхем памяти реализовать установленную задержку, поэтому выбор здесь неоднозначен.

DRAM RAS Precharge Time

Параметр, определяющий время повторной выдачи (период накопления заряда, подзаряд) сигнала RAS#, т.е. через какое время контроллер памяти будет способен снова выдать сигнал инициализации адреса строки. Это связано с необходимостью проведения фаз обновления содержимого ячеек памяти. Данная установка может принимать значения 3 или 4 (в циклах шины), и во временном отношении аналогична предыдущей — чем меньше, тем лучше. Иногда возможен вариант, когда можно выставить конкретную схему циклов регенерации или прямо указать время обновления содержимого строки памяти, выражаемое в микросекундах (ms).

Для поддержания целостности информации заряд конденсаторов следует периодически обновлять (регенерировать), читая содержимое всего ряда целиком и заново перезаписывая. Устройствам памяти с динамической “природой” присущ один довольно серьезный недостаток — высокая вероятность образования ошибки, когда данные, записанные в определенную ячейку, при считывании могут оказаться иными, что связано с циклами регенерации заряда в ячейке памяти. Для контролирования и исправления этого недостатка существует два способа проверки целостности данных: контроль бита четности и код коррекции ошибок. Как уже упоминалось, элементарная ячейка динамической памяти состоит из одного конденсатора и запирающего транзистора, что дает возможность достичь большей плотности размещения элементов (большее количество ячеек на единицу площади) по сравнению со статической. С другой стороны, данная технология имеет ряд недостатков, главным из которых является то, что заряд, накапливаемый на конденсаторе, теряется со временем. Несмотря на то, что при топологии конденсаторов ячеек динамической памяти используется хороший диэлектрик с электрическим сопротивлением в несколько тераом (х1012 Оhm), заряд теряется достаточно быстро, так как размеры одного конденсатора микроскопические, а емкость мизерна — порядка 10-15 F. При такой емкости на одном конденсаторе накапливается всего порядка 40000 электронов.

Среднее время утечки заряда в массиве ДОЗУ составляет порядка сотни или даже десятков миллисекунд, поэтому его необходимо перезаряжать с 64ms интервалом, согласно требованиям JEDEC Std 21-C. Данные из ядра считываются и передаются на усилители уровня, после чего, не поступая на выход, записываются обратно в массив. Стандартно, банк микросхемы памяти (массив ячеек, имеющий определенную организацию структуры, состоящей из строк и столбцов) содержит или 2k, или 4k, или 8k строк (точнее, или 2048, или 4096, или 8192), доступ к которым позволяет производить одновременную регенерацию всего массива, относящегося к этой строке. Как бы то ни было, наилучшая схема регенерации заключается не в одновременном обновлении содержимого ячеек всех строк, а в поочередном обновлении индивидуально каждой строки. В результате, взяв за основу 4k-массив (средняя плотность), можно вычислить стандартную нормальную схему регенерации одной строки, поделив полный цикл обновления на количество строк: 64000ms/4096=15.625ms. В случае, если банк содержит более 4k строк, любые две строки могут обрабатываться одной командой, или все решается простым кратным увеличением частоты регенерации — с точностью до наоборот, если банк содержит менее 4096 строк. Если рассматривать возможные варианты решения проблемы обновления содержимого массива ДОЗУ, на данный момент известны три различных метода регенерации данных.

Регенерация одним RAS (ROR — RAS Only Refresh). В данном случае адрес регенерируемой строки передается на шину адреса, в ответ на что выдается сигнал RAS# (точно так же, как при чтении или записи). При этом выбирается строка ячеек, и данные из них временно поступают на внутренние цепи (точнее, на выходные усилители уровня) микросхемы, после чего записываются обратно. Так как сигнала CAS# не следует, цикл чтения/записи не начинается. В следующий раз передается адрес следующей строки и так далее, пока не восстановятся все ячейки, после чего цикл регенерации повторяется. Недостатком этого метода, безусловно, является то, что занимается шина адреса, и в момент регенерации блокируется доступ к другим подсистемам компьютера. Это сильно снижает общую производительность, поскольку подобного рода регенерацию в микросхемах памяти необходимо осуществлять довольно часто.

CAS перед RAS (CBR — CAS Before RAS). При нормальном цикле чтения/записи сигнал RAS# всегда приходит первым, а за ним следует CAS#. Если же CAS# приходит раньше RAS#, то начинается специальный цикл регенерации (CBR), при котором адрес строки не передается, а микросхема использует свой собственный внутренний счетчик, содержимое которого увеличивается на 1 (дискретное инкрементирование) при каждом цикле CBR. Этот режим позволяет регенерировать память не занимая шину адреса, что, безусловно, более экономично в плане использования системных ресурсов.

Механизм автоматической регенерации (AutoPrecharge) или саморегенерации (SEREf — SElf REfresh) обычно используется в режиме энергосбережения, когда система переходит в состояние “сна” и формирователь синхросигналов деактивируется. Режим расширенной регенерации (EREf — Extended REfresh) не является отдельным методом, характеризующим саму способность микросхемы, а, как и сокращенная (REREf — REduce REfresh), определяет только режим периодичности обновления содержимого массива относительно нормального цикла (Normal, 15.625ms), и состоит в “подмножестве” цикла саморегенерации. При EREf энергия экономится потому, что теперь регенерацию страницы (строки) можно производить значительно реже: скажем, через 125.2ms, а не через 15.625ms, как это происходит при стандартной регенерации. Сокращенная регенерация рекомендуется к использованию в микросхемах памяти большой емкости (64Mbit устройства и более емкие) и в модулях памяти с большим количеством микросхем (16 и более). Саморегенерация используется в периоды микропотребления (общее состояние системы — Suspend), когда содержимое микросхемы памяти регенерируется самостоятельно путем инкрементирования своего внутреннего счетчика — это значит, что все функции управления можно выключить. В таком состоянии обновление данных в ячейках по вышеописанным методам невозможно, потому как некому посылать сигналы на регенерацию, и микросхема памяти делает это сама — в ней запускается свой собственный генератор, который тактирует ее внутренние цепи.

Так, метод ROR использовался еще в первых микросхемах DRAM и на данный момент практически не применяется. Метод CBR активно используется в микросхемах EDO DRAM. Саморегенерация рекомендована для систем на основе SDRAM и поддерживает значения: 3.906ms (0.25х-сокращенная), 7.812ms (0.5х-сокращенная), 15.625ms (нормальная), 31.25ms (2х-расширенная), 62.5ms (4х-расширенная) и 125.2ms (8х-расширенная). Понятно, что сама способность конкретной микросхемы памяти (контролируемая со стороны “закрытых” установок в BIOS или саморегенерация) определяется архитектурно и зависит от типа используемой памяти. Однако выставив наибольший временной цикл, можно “не вписаться” в общую временную диаграмму, поэтому производитель модуля памяти такого рода информацию просто заносит в специально отведенное место — микросхему SPD, которой оснащено большинство современных модулей DIMM. В случае, если таковой микросхемы на используемом модуле нет, то можно, при условии, что это позволяет гибкая настройка BIOS Setup, самостоятельно выставить периодичность проведения регенерации, исходя из стандартных 15.625ms для 4k массива банка, кратно уменьшая (сокращенная) цикл при увеличении количества строк, или увеличивая (расширенная) цикл при уменьшении количества строк — все зависит от логической организации (количество банков и структура банка) микросхемы и их количества в конкретном модуле памяти.

MA Wait State

Период ожидания до переключения адреса, который позволяет установить или снять дополнительный такт задержки до начала обращения к конкретной микросхеме памяти (подача сигнала выбора кристалла, CS#). Своего рода “контрольной точкой” срабатывания является переключение сигнала MA# (Memory Address) с одно- или двухтактным опережением CS#. Более подробно этот пункт будет рассмотрен ниже применительно к синхронным системам.

DRAM R/W Leadoff Timing

Данный пункт характеризует число тактов, затрачиваемое подсистемой памяти при подготовке выполнения операции чтения/записи данных, определяя их количество на шине до выполнения операции в самой микросхеме. При этом возможны следующие значения: 8/7 и 7/5 — количество тактов для чтения/записи соответственно. Как и любой параметр, характеризующий задержку, его необходимо стараться установить с меньшим значением.

Speculative Leadoff

Параметр, включающий (Enable) и выключающий (Disable) режим опережающей выдачи сигнала чтения (READ), разрешение которого позволяет выдавать его немного ранее, чем адрес будет декодирован (однозначно определен при помощи стробов RAS# и CAS#). Поскольку на определение адреса необходимой ячейки требуется определенное время, система теряет такты, которые могут использоваться с пользой. Поэтому включение этого параметра дает возможность считать следующий адрес ячейки, пока идет процесс определения координаты ячейки, адрес которой считался ранее. Данный прием также позволит в некоторой степени сэкономить время и уменьшить количество “холостых” тактов системной шины.

DRAM ECC/Parity Select

Параметр, управляющий режимами контроля целостности данных: кода коррекции ошибки (ECC — Error Correction Code) и проверки четности (Parity). Нередко встречается также пункт “DRAM Data Integrity Mode”.

По характеру ошибки памяти можно разделить на два типа. Временные ошибки (сбои, Soft Errors), связанные с воздействием космических лучей, альфа-частиц, посторонних и внутренних шумов, приводят обычно к однократному изменению информации, и чаще всего данные записываются в ту же ячейку повторно без ошибок. Постоянные ошибки (отказы, Hard Errors), возникающие вследствие неисправности самих микросхем памяти, зачастую приводят к потере информации в целом столбце или даже во всей микросхеме.

В случае использования схемы Parity один бит четности сохраняется в специально выделенной области памяти вместе с каждыми восемью битами информации. Бит четности формируется так: подсчитывается количество “единиц” в двоичном представлении байта: если оно четное, то данный бит принимает значение “1”, если нет — “0”. После этого данные записываются в оперативную память. При считывании этого байта данных из ячейки к нему “приписывается” бит четности и затем анализируется 9bit значение. Если в этом числе нечетное количество единиц, то бит четности “обрезается” и байт информации передается на обработку — в противном случае генерируется ошибка четности и работа компьютера приостанавливается с выдачей сообщения. Если изменено четное количество бит информации, проверка бита четности не сработает. Однако, несмотря на то, что схема контроля четности может выявлять максимум двухбитные ошибки, исправлять их она не способна.

Механизм ECC может не только выявлять, но и исправлять ошибки, а также генерировать ошибку четности. Обычно данная схема работы основывается на использовании кодов Хемминга (помехоустойчивые коды), позволяющих выявлять и исправлять один неверный бит или же найти две и исправить одну ошибку (корректирующие свойства кода определяются его избыточностью). Коррекция ошибок намного сложнее контроля четности и используется в системах, где необходима передача большого количества информации с минимальной вероятностью ошибки. В любом случае, будь то схема Parity или ECC, использование данных типов памяти может снизить производительность: если контроль четности может “затормозить” систему на 2—3 %, то у ECC этот показатель иногда доходит до 10% в зависимости от сложности используемого алгоритма. Кроме этого, 72bit модуль ECC дороже своего обычного 64bit “аналога” при условии одинаковой емкости, поэтому выбор использования данных типов памяти на ПК является исключительно делом каждого.

Наличие в ПК модуля, поддерживающего схему ECC, определяется самой системой, и если таковые не обнаружены, пункт меню “DRAM Data Integrity Mode” изменить невозможно — “серое” поле с индикацией “Non-ECC”. Разрешение (Enable) же пункта “DRAM ECC/Parity Select” при условии, что в системе используются соответствующие модули памяти, приводит к активации контроля коррекции ошибки или к включению механизма контроля четности.

SDRAM Configuration

Параметр, определяющий способ настройки подсистемы памяти на основе SDRAM и принимающий значения: by SPD (необходимые параметры считываются из специальной микросхемы последовательного детектирования, устанавливаемой на модуле памяти, и полностью оптимально согласованы с типом и индивидуальными характеристиками установленных на нем микросхем) или Manual (разрешено варьировать определенные параметры “вручную”, причем соответствующие пункты меню этих параметров становятся доступными для изменения). Суть данной установки сводится к тому, что в случае использования схемы Manual разрешается доступ к изменению параметров “SDRAM CAS Latency Time”, “SDRAM RAS-to-CAS Delay” и “SDRAM RAS Precharge Time”, которые образуют основную тайминговую схему работы памяти (CL-tRCD-tRP соответственно) и позволяют осуществлять более гибкую настройку подсистемы на основе синхронного ДОЗУ — все аналогично рассматриваемому ранее параметру “Auto Configuration”. В случае использования схемы SPD требуемые значения автоматически загружаются из микросхемы EEPROM, в которой производитель конкретного модуля памяти заранее “прошивает” необходимые значения временных параметров (таймингов), гарантируя стабильную работу.

При синхронной работе с памятью операции выполняются строго с тактами системного генератора. При этом само управление синхронного ДОЗУ несколько усложняется относительно асинхронного, поскольку приходится вводить дополнительные защелки, хранящие адреса, данные и состояния сигналов управления. В результате этого вместо продолжительности цикла доступа, применяющегося для характеристики в асинхронных системах, для описания быстродействия SDRAM прибегают к указанию длительности периода синхросигнала (tCLK — Clock time — величина, обратно пропорциональная частоте следования синхроимпульсов). Поэтому в некоторых разновидностях BIOS возможно указание непосредственно длительности периода синхросигнала: 7ns (максимальная частота функционирования данного модуля — 143MHz, следовательно, используемые временные схемы будут оптимизированы для устройств памяти с параметром -7, указываемом непосредственно на самой микросхеме), 8ns (максимальная частота функционирования данного модуля — 125MHz, поэтому временные установки будут оптимизированы для приборов памяти с параметром -8) и 10ns (максимальная частота функционирования данного модуля — 100MHz, поэтому временные установки будут оптимизированы для микросхем памяти с параметром -10), которые работают аналогично описываемым ранее в пункте “Auto Configuration”, но встречаются сравнительно редко.

Стандартно, массив микросхемы содержит логические банки (Bank), количество и организация которых определяется индивидуальностью (фундаментальностью) самой архитектуры и конечной емкостью микросхемы. Банки содержат логические строки (Row), называемые также страницами (Page, во избежание путаницы с физическими строками), которые, в свою очередь, содержат столбцы (Column) — матрица, образуемая такой иерархией, и является ядром микросхемы памяти. Строка — это объем считываемых или записываемых данных в один из нескольких банков ядра. Столбцы — подмножества строк, которые считываются или записываются в индивидуальных фазах операций чтения/записи.

Рассмотрим последовательно продвижение данных по микросхеме. Обычно цикл начинается по приходу команды активизации банка, которая выбирает и активирует необходимый банк и строку в его массиве. В течение следующего цикла информация передается на внутреннюю шину данных и направляется на усилитель уровня (как говорилось ранее, своего рода “накопитель”, играющий роль как усилителя сигнала, так и временного буфера). Когда усиленный уровень сигнала достигает необходимого значения, данные запираются (Latch) внутренним синхросигналом – этот процесс, именуемый задержкой между определением адреса строки и столбца (tRCD — RAS#-to-CAS# Delay), занимает 2—3 цикла системной шины (количество периодов синхросигнала). После этой задержки команда чтения может подаваться совместно с адресом столбца, чтобы выбрать адрес первого слова (в данном случае, объем данных, передаваемых за один цикл, равный ширине шины данных микросхемы памяти), которое надо считать с усилителя уровня. После выставления команды чтения выполняется двух- или трехтактная задержка строба выбора столбца (задержка сигнала CAS# — CAS# Latency или просто CL), в течение которой данные, выбранные из усилителя уровня, синхронизируются и передаются на внешние выводы микросхемы (линии DQ). За первым словом следуют остальные в течение каждого последующего синхросигнала, отрабатывая полную установленную длительность пакета (Burst Length) — количество непрерывно передаваемых слов за одну фазу передачи данных. Лишь после того, как вся информация передалась, данные можно возвратить обратно из усилителя в строку пустых ячеек массива для восстановления его содержимого, что занимает 2—3 тактовых цикла. Справедливости ради необходимо заметить, что вопреки правильной записи последовательности tRCD-CL-tRP обычно основная тайминговая схема имеет вид CL-tRCD-tRP, таким образом указывая степень важности составляющих ее параметров. Динамический, а значит обладающий свойством ослабевания сигнала и утечки, по своей природе массив ячеек должен регенерировать их содержимое. Периоды восстановления заряда устанавливаются регенерирующим контроллером программы мониторинга, выполняемой счетчиком регенерации (Refresh Counter) — подобное восстановление требует 7—10 циклов, в течение которых поток данных прерывается.

Процедура записи в рассмотрении временной схемы доступа аналогична фазе чтения с разницей в дополнительном интервале tWR, характеризующем период восстановления интерфейса после проведения операции. Иными словами, период восстановления в фазе записи — это обычно двухтактная задержка между окончанием выдачи данных на шину (последний импульс по Data Bus) и инициированием нового цикла. Этот временной интервал обеспечивает восстановление интерфейса после проведения операции записи и гарантирует корректность ее выполнения. В результате, по окончанию передачи последнего слова в фазе записи, строка банка, к которой происходит обращение, входит в стадию регенерации не сразу, а по истечении дополнительной задержки, минимальное значение которой обуславливается наименьшим интервалом, в течение которого ожидается корректное завершение текущей операции записи. Поэтому время активности страницы в фазе записи становиться больше значения tRAS фазы чтения на длительность периода восстановления, tWR.

SDRAM CAS Latency Time

Задержка выдачи сигнала CAS# для микросхемы синхронного ДОЗУ является одной из важнейших характеристик и обозначает минимальное количество циклов шины (Clock Period) от момента “фиксации” запроса данных стробом CAS# до момента их устойчивого определения и считывания. Предполагается, что на момент прихода фронта сигнала CAS# на адресных входах имеются правильные данные. Однако, поскольку везде существуют временные задержки (в том числе и внутри самой микросхемы), то специально отводится некоторое время на их преодоление, причем в силу разброса параметров задержки для разных адресных линий могут быть разными — это и есть в данном случае CAS Latency (CL), а CL2 и CL3 — время вводимой задержки в тактах (2 и 3 соответственно). Чем меньше задержка — тем больше скорость работы с памятью, но и тем больше риск, что данные попадут “не по адресу”, что непременно вызовет сбой. Устойчивость к подобным сбоям — есть устойчивость по CL.

Иными словами, CL — это задержка между формированием логикой управления кристалла микросхемы команды чтения и доступностью к чтению первого слова. Если регистрация (опознавание приемником сигнала конкретного логического уровня) команды чтения происходит по фронту такта N, а CL составляет M тактов, то соответствующие данные будут доступны через N+M тактов. Однако, для обеспечения гарантированной выдачи данных, транзисторы выходных цепей линий данных включаются на один такт раньше (N+M-1), т.е. на них выводятся данные с неопределенными (на тот момент) уровнями, в результате чего контроллер памяти ожидает еще один такт, и только после этого принимает поступающие данные. При использовании CL2 для модулей, рассчитанных для данной частоты на CL3, выходные цепи могут не успеть выставить нужный уровень (и обеспечить номинальный ток) для точного представления данных на шине и может возникнуть ошибка.

SDRAM RAS-to-CAS Delay

Аналогичного рода параметр (Fast RAS-to-CAS Delay), определяемый как tRCD, описывался ранее, и в данном случае может принимать значения 2 или 3, устанавливая двух- и трехтактную задержку от начала передачи команды активизации конкретного логического банка до момента приема команды чтения/записи по приходу фронта CAS# (переход в активный низкий уровень). Другими словами, после подачи команды активизации банка, строку, к которой происходит обращение, необходимо предварительно зарядить (выполнить цикл накопления заряда, Precharge) до момента поступления команды чтения (определяемой адресом столбца). Это означает, что данные передаются из массива памяти на внутрикристальный выходной усилитель уровня с задержкой 2 или 3 цикла. Необходимо понимать, что рассматриваемая задержка сама по себе играет довольно незначительную роль в общей задержке при условии попадания в страницу и/или чтения данных из открытой страницы. Тем не менее, далеко не в каждом BIOS можно варьировать значение данной задержки по причине отсутствия соответствующего параметра, однако в действительности tRCD учитывается также в значении “Bank X/Y Timing”.

SDRAM RAS Precharge Time

Длительность подзаряда строки — tRP. В данном случае микросхема DRAM с двумя/четырьмя банками (логическая организация) позволяет “скрыть” это время, чтобы обеспечить непрерывный ввод/вывод данных: в то время, когда происходит какая-либо операция с одним банком памяти, другой успевает регенерировать (обновить данные). Проще говоря, данный параметр позволяет определять быстрое (Fast) или медленное (Slow) накопление заряда по линии RAS# до начала цикла регенерации. Установка значения Fast увеличивает быстродействие, однако может привести к нестабильности работы. Slow же действует наоборот — повышает стабильность работы компьютера, однако увеличивает время, затрачиваемое на цикл регенерации данных. Поэтому рекомендуемое значение Fast следует устанавливать в случае уверенности в качестве микросхем памяти. Обычно встречаемые значения 2 и 3 данного пункта определяют количество тактов системной шины, необходимых для восстановления данных в странице, к которой происходило обращение.

Вообще, задержка, обуславливаемая накоплением заряда в строке, необходима для перемещения данных обратно в массив (закрытие банка/страницы) до момента прихода команды активизации следующего банка. Так, 30—60 % от общего количества передаваемых запросов на чтение теряется в пределах одной страницы (Page), стандартно называемая строкой логического банка), что получило название попадания в страницу (Page Hit). Поэтому в данном случае нет необходимости активизировать банк, так как данные уже находятся в странице, и все, что требуется — это изменить адрес столбца посредством выдачи сигнала CAS#. Если запрашиваемые данные не найдены в пределах данной страницы, их необходимо вернуть обратно в массив и закрыть банк.

Если запрашиваемые данные существуют в одном и том же банке, но в разных строках, необходимо подать команду перезаряда, чтобы банк закрылся (промежуток, составляющий длительность подзаряда), а новая команда активизации банка откроет правильную строку (задержка tRCD), где размещаются необходимые данные. Позднее, через промежуток CL, команда чтения придет по правильно выбранному адресу. В результате количество циклов общей задержки (схема tRCD-CL-tRP), описываемое как 2-2-2, составляет 6 тактов, а схема 3-3-3 увеличивает ее до 9.

Если запрашиваемые данные расположены в разных строках, нет необходимости тратить время на ожидание закрытия первого банка, поэтому задержка tRP в данном случае не учитывается. Следовательно, остается только задержка выдачи сигнала CAS# и интервал RAS#-CAS#. Вообще, данная схема немного упрощена, поскольку если данные находятся в одном банке, но в разных строках, то банк необходимо не просто закрыть, а еще и реактивировать. Поэтому каждый банк имеет очень малое время, в течение которого он остается открытым, и длительность цикла tRC становится довольно критическим фактором.

Для микросхемы памяти, которая вошла в фазу саморегенерации (SEREf), необходим определенный интервал времени для ее возвращения обратно в активное состояние. Как уже говорилось ранее, в случае ввода устройства в фазу Self-Refresh все входные интерфейсы переводятся в состояние DtC (Don’t Care), а тактовый вход CKE деактивируется, после чего моментально включается внутрикристальный счетчик регенерации. В этот период микросхема памяти является пассивным относительно системы устройством и не отвечает на команды, поскольку интерфейс синхронизации деактивирован. После проведения фазы внутренней регенерации механизм внешней синхронизации активизируется и устройство возвращается в активное состояние по команде Refresh Exit. Тем не менее, полная фаза активизации с момента начала подачи сигнала CKE до готовности принять первую команду от контроллера занимает 4—7 тактов и называется Refresh RAS Assertion.

SDRAM Cycle Time Tras/Trc

Параметр, характеризующий быстродействие микросхемы SDRAM (динамику массива) и определяющий отношение интервала, в течение которого строка открыта для переноса данных (tRAS — RAS# Active time), к периоду, в течение которого завершается полный цикл открытия и обновления ряда (tRC — Row Cycle time), также называемого циклом банка (Bank Cycle Time).