Перейти к контенту

Инструкции

Время чтения 2 мин.Просмотры 219Опубликовано 30.03.2023

В Мультисиме можно программировать схемы благодаря триггерам. Это запоминающие логические элементы, способные долго находиться в одном из двух состояний и переключаться между ними в зависимости от входящего сигнала. Их состояние определяется по величине выходного напряжения, которое изменяется скачкообразно – за короткий промежуток времени. По этой причине триггер относят к импульсным устройствам.

Разнообразие

В Multisim можно смоделировать все виды логических переключателей.

D-триггер – запоминает состояние на входе и дублирует его на выходе. Имеет два вывода: информационный (вход) и синхронизации (выход). Строится на шести логических элементах, применяется для деления частоты.

Его построение в Multisim смотрите ниже.

RS-триггер – асинхронный компонент, запоминающий состояние всех выводов при неактивности и изменяет его при подаче напряжения. На видео показано, как построить эмуляцию этого логического элемента в Мультисиме.

Триггер Шмидта – при подаче сложного аналогового сигнала меняет своё состояние.

T-триггер – счётный элемент с одним входом, он изменяет состояние с каждым поступающим импульсом.

Схема эмуляции показана на видео.

JK– универсальный триггер, на его основе строится любой из запоминающих состояние элементов. При подаче двух единиц на входы он инвертирует сигнал.

В программе нет готовых триггеров, поэтому их работу придётся эмулировать вручную.

Цифровыми

называют устройства, предназначенные

для формирования, преобразования и

передачи кодовых слов. При этом кодовые

слова (коды или числа) в электронных

цифровых устройствах представляются

в виде последовательностей электрических

импульсов (сигналов с двумя уровнями

напряжения: высоким и низким), а их

преобразования осуществляются

арифметическими, логическими, запоминающими

и вспомогательными устройствами.

Элементами

и узлами цифровых устройств, служащими

основой для построения микропроцессоров,

микропроцессорных систем, компьютеров,

автоматизированных систем управления

объектами, технологическими процессами

и информационными потоками являются:

дешифраторы, сумматоры, триггеры,

регистры, счетчики и многие другие.

Базовые

элементарные единицы цифровых схем,

такие как элементы «И», «ИЛИ», «НЕ»,

находятся в разделе Misc

Digital,

подраздел TIL.

Рассмотрим

каждый из них в отдельности:

|

|

Элемент |

|

|

Элемент |

|

|

Элемент |

|

|

Элемент |

|

|

Элемент |

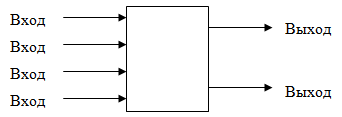

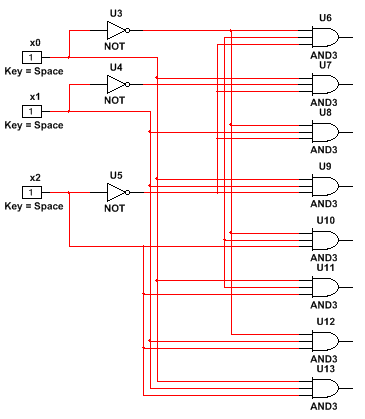

На

основе базовых элементов создадим схему

цифрового устройства для принятия

решения по условию. Блок-схема такого

устройства представлена на рис. 6.22.

Условие будет задано логическим

выражением:

![]()

Рис.

6.22. Блок-схема цифрового устройства

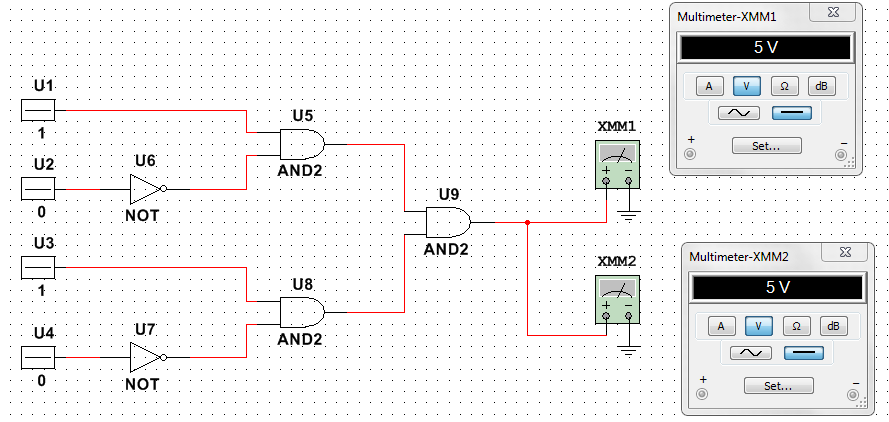

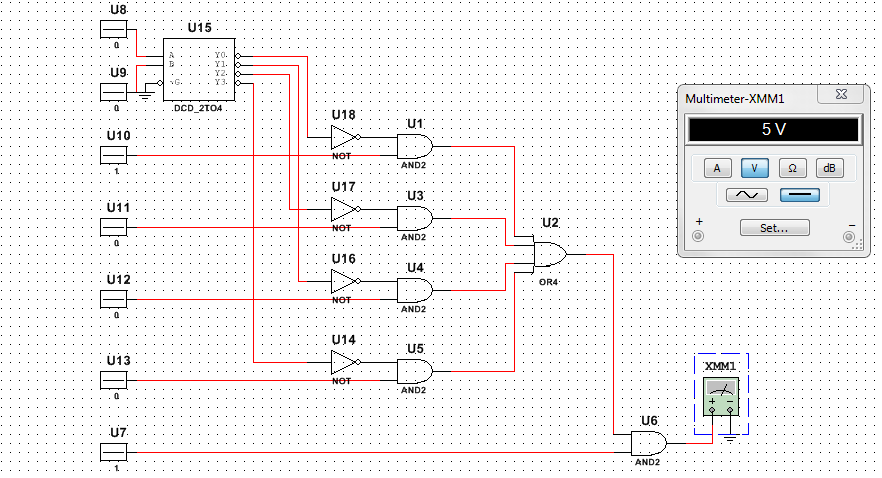

Модель, полученная

в Multisim, отображена на рис. 6. 23. На выходах

будет наблюдаться сигнал высокого

уровня (5В), когда конфигурация входов

будет удовлетворять заданному условию.

Рис.

6.23. Модель устройства в Multisim

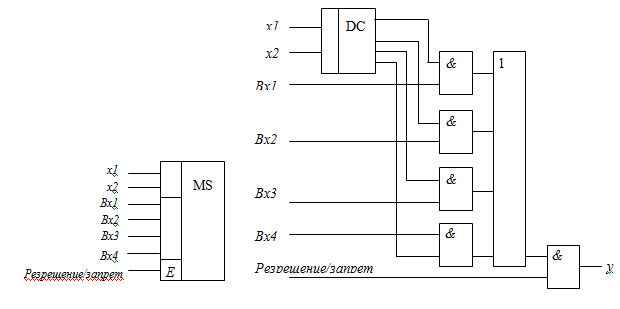

Теперь рассмотрим

схему и механизм работы часто используемого

устройства – мультиплексора –

переключателя каналов. Структурная

схема отображена на рис. 6.21. На схеме

есть два базовых элемента – переключатель

и выключатель. Переключатель выполнен

в виде ключа с сигналами x1 и x2, именно

он определяет, какой из четырех каналов

подключен к выходу в данный момент. В

положении ключа 00 (код адреса х1 = 0, х2 =

0) у = а; в положении 01 (х1 = 0, х2 = 1) у = b; в

положении 10 (х1 = 1, х2 = 0) у = c; в положении

11 (х1 = 1, х2 = 1) у = d. Выключатель контролирует

работу устройства в целом: при Е = 1

мультиплексор работает как обычно, при

Е = 0 выход узла находится в неактивном

состоянии, мультиплексор заперт.

Функционирование мультиплексора

описывается выражением:

![]()

Рис.

6. 24. Структурная схема мультиплексора

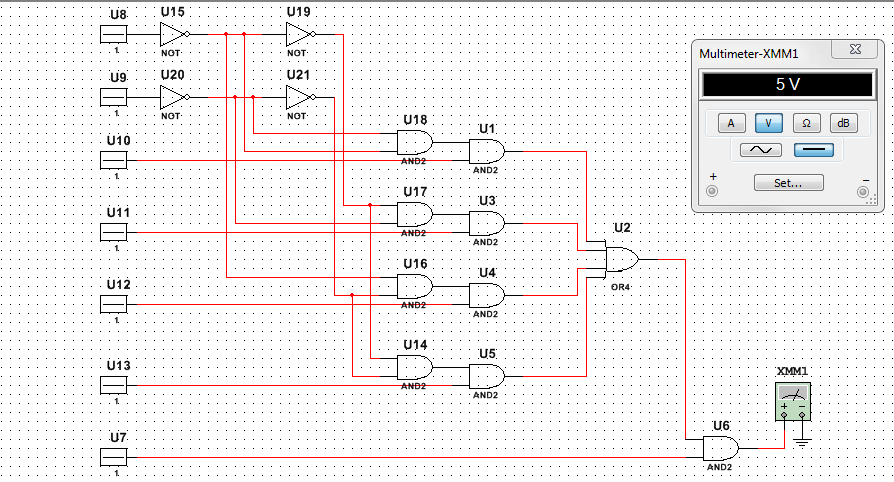

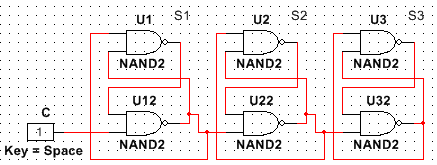

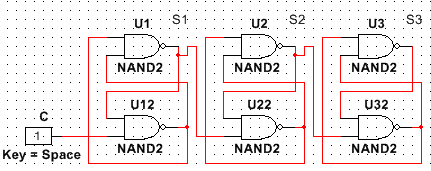

На рис. 6.25 а, б

приведены два примера реализации модели

мультиплексора. В первом случае ключ

состоит из двух линий, в каждой из которых

по два последовательно включенных

элементов «НЕ». Во втором – используется

дешифратор DCD_2TO4.

Рис.

6.25 а. Модель мультиплексора

Рис.

6.25 б. Модель мультиплексора

Триггеры.

Триггерами

называются устройства, обладающие двумя

устойчивыми состояниями (Q

= 1 иQ = 0) и

способные находиться в одном из них

сколь угодно долго и переходить из

одного состояния в другое под воздействием

внешних сигналов. В каком из этих

состояний окажется триггер, зависит от

сигналов на входах триггера и от его

предыдущего состояния, т.е. он имеет

память. Таким образом, триггер –

элементарная ячейка памяти.

Т ип

ип

триггера определяется алгоритмом его

работы, в зависимости от которого триггер

может иметь установочные, информационные

и управляющие входы. Установочные входы

обуславливают состояние триггера

независимо от состояния других входов.

Входы управления разрешают запись

данных, подающихся на информационные

входы. Наиболее распространенными

являются триггерыRS-,JK–,D–

иT-типов.

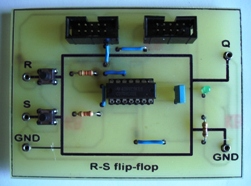

RS-триггер– простейший автомат с памятью, который

может находиться в двух состояниях.

Триггер имеет два установочных входа:

установкиS(set– установка) и сбросаR(reset– сброс), на которые

подаются входные сигналы от внешних

источников. При подаче на установки

активного логического уровня триггер

устанавливается в единицу (Q= 1,Q′ = 0, здесь штрих

означает инвертирование), при подаче

активного уровня на вход сброса триггер

устанавливается в ноль (Q= 0,Q′ = 1). Если на оба

установочных входа подать пассивный

логический уровень, то триггер сохраняет

предыдущее состояние выходов:Q

= 1 илиQ = 0. Каждое

состояние устойчиво и поддерживается

за счет действия обратных связей. Подача

активного уровня одновременно на оба

установочных входа запрещена, так как

триггер не может быть установлен в ноль

и единицу.

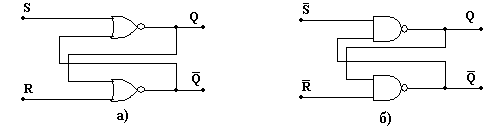

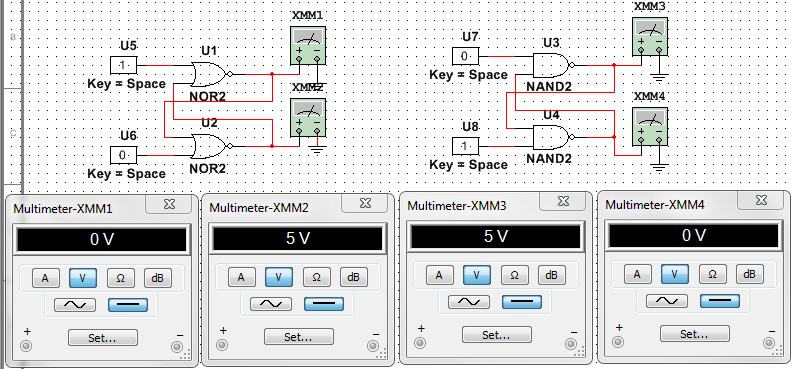

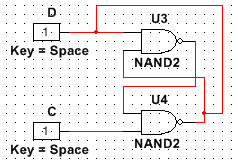

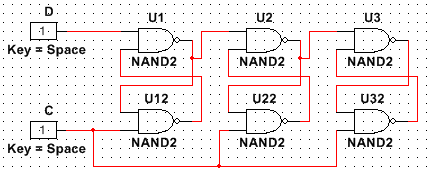

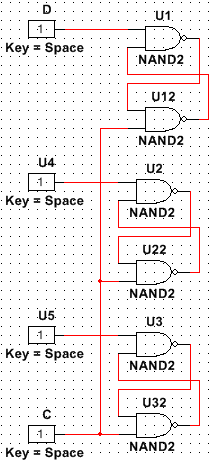

RS-триггер

может быть выполнен на элементах «ИЛИ-НЕ»

или «И-НЕ» (рис. 6.26).

а

б

Рис.

6.26. RS-триггер:

а –

на элементах «ИЛИ-НЕ», б

– на элементах

«И-НЕ»

Рис.

6.26. Моделирование RS-триггера в Multisim

Для RS-триггеров,

выполненных на элементах «ИЛИ-НЕ»,

активным уровнем на управляющих входах

является уровень логической единицы,

а на элементах «И-НЕ» – уровень

логического нуля.

RS-триггер

– основной узел построения последовательных

схем. Условия переходов триггеров из

одного состояния в другое можно описать

табличным, аналитическим или графическим

способами. Табличное описание работыRS-триггера на элементах

«ИЛИ-НЕ» и «И-НЕ» представлено в табл.

6.1 и 6.2 соответственно, где Qt– предшествующее состояние выхода;Qt+1– новое состояние, устанавливающееся

после перехода; – – неопределенное

состояние.

Т а б л и ц а

6.1 Т а б л и ц

а 6.2

-

R

S

Qt+1

R

S

Qt+1

0

0

Qt

0

0

–

1

0

0

1

0

1

0

1

1

0

1

0

1

1

–

1

1

Qt

Триггер JK-типаимеет более сложную структуру и более

широкие возможности по сравнению вRS-триггером. Кроме

информационных входовJиKи прямого и

инверсного выходовQиQ′,JK-триггер

имеет вход управленияC(тактирующий или счетный) и два асинхронных

установочных входаRиS. Обычно активными

уровнями установочных сигналов являются

нули. Установочные входы имеют приоритет

над остальными входами. Активный уровень

сигнала на входеSустанавливает триггер в состояние

единица (Q = 1), а на

входеRв состояние

ноль (Q = 0), независимо

от сигналов на остальных входах. Если

на входы установки подать пассивный

уровень сигнала, то состояние триггера

будет изменяться по фронту импульса на

счетном входе в зависимости от состояния

входовJиK.

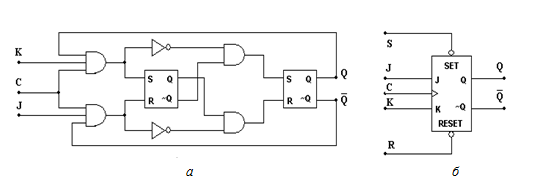

Один из вариантов

функциональной схемы JK-триггера

и его условное графическое изображение

приведены на рис. 6.27, временные

диаграммы его работы приR=S=1

– на рис. 6.28.

Рис.

6.27. JK-триггер:

а

– функциональная схема; б

– условное

графическое обозначение

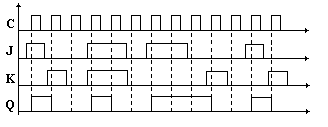

Рис.

6.28. Временная

диаграмма работы JK-триггера

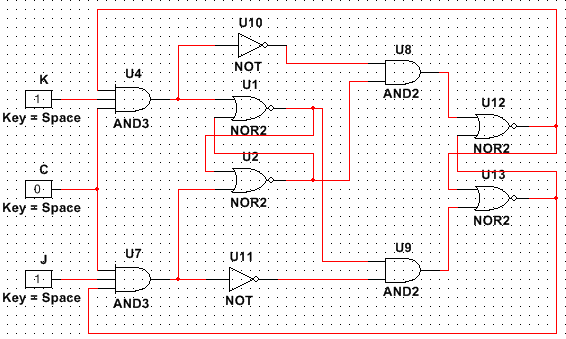

Рис.

6.29. Моделирование JK-триггера в Multisim

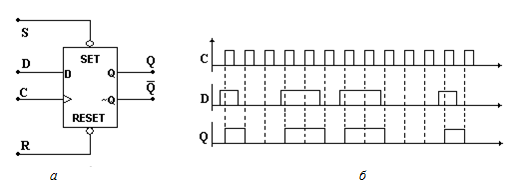

D -триггеримеет один информационный входD(data– данные) и один

-триггеримеет один информационный входD(data– данные) и один

счетный входC.

Информация с входаDзаписывается в триггер по положительному

перепаду импульса на счетном входе и

сохраняется до следующего положительного

перепада. Кроме счетногоCи информационногоDвходов, у триггера есть два асинхронных

установочных входаRиS. Установочные

входы приоритетные. Активный уровень

сигнала на входеSустанавливает триггер в состояние

единица (Q=1), а на входеRв состояние ноль

(Q=0), независимо от сигналов

на остальных входах.

Условное обозначение

D-триггера с диаграммами

входных и выходных сигналов приведено

на рис. 6.30.

Рис.

6.30. D-триггер:

а –

условное обозначение; б

– временные

диаграммы

Рис.

6.31. Моделирование D-триггера в Multisim

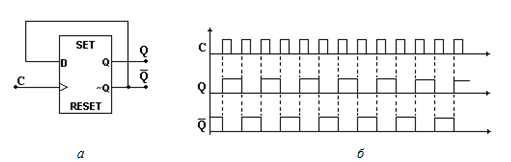

T -триггер,

-триггер,

илисчетный триггер, – устройство,

осуществляющее счетный режим. Такие

схемы можно построить на основеJK–

илиD-триггеров.

В D-триггере

счетный режим (рис. 6.32,а) реализуется

при помощи обратной связи, когда на

входDподается сигнал

с инверсного выхода триггера, т.е. всегда

осуществляется неравенство сигналов

на входеDи на выходеQ(еслиQ=1,D=0 и наоборот). Следовательно, при

каждом положительном перепаде сигнала

на счетном входеСсостояние выхода

будет изменяться на противоположное.

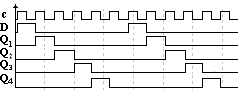

Рис.

6.32. T-триггер:

а –

условное обозначение; б

– временная

диаграмма

Таким образом, на

каждые два входных тактовых импульса

T-триггер формирует

один период выходного сигналаQ,

т.е. период выходного сигнала в два раза

больше периода входного сигнала.

Следовательно, триггер осуществляет

деление частотыfтна его входе на две:fQ=fт/2, гдеfQ– частота следования импульсов на

выходе триггера.

Рис.

6.33. Моделирование T-триггера

в Multisim

Регистры.

Т риггерным

риггерным

регистром называется совокупность

триггеров с определенными связями между

ними, при которых они действуют как

единое устройство. Регистры выполняются

на синхронных триггерахJK–

илиD-типа. В зависимости

от выполняемых функций регистры делятся

на накопительные (параллельные) и

сдвигающие.

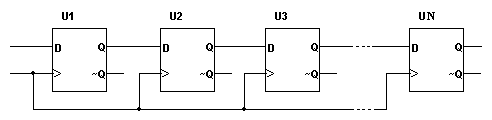

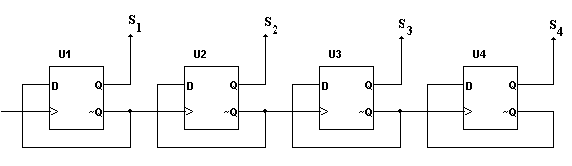

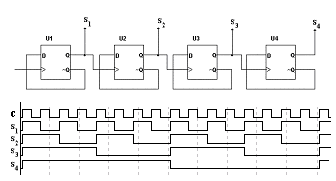

В последовательном

регистре выход предыдущего триггера

подается на вход следующего триггера,

а тактовые импульсы подаются на входы

Свсех триггеров, составляющих

регистр, одновременно (рис. 6.34). При этом

содержимое каждого триггера записывается

в последующий триггер. Такие регистры

называются сдвиговыми регистрами, или

регистрами сдвига.

Рис.

6.34. Последовательный

регистр (регистр сдвига)

Рис.

6.35. Моделирование последовательного

регистра в Multisim

Если на вход Dрегистра сдвига подать единицу, а на

входСтактовую частоту, то единица

начнет продвигаться по регистру сдвига,

т.е. под воздействием первого тактового

импульса единица запишется в первый

триггер регистра. Под воздействием

второго тактового импульса эта единица

перепишется во второй триггер и т.д.,

когда под воздействиемN-го

тактового импульса единица не выйдет

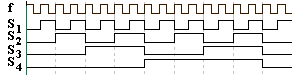

из регистра сдвига. Временная диаграмма

работы четырехразрядного регистра

сдвига приведена на рис. 6.36.

Рис.

6.36. Временная

диаграмма четырехразрядного регистра

сдвига

Виды регистров

сдвига:

-

с последовательным

вводом и выводом; -

с последовательным

вводом и параллельным выводом; -

с параллельным

вводом и последовательным выводом; -

с

Рис.

6.37. Параллельный

регистрпеременным направлением

сдвига (реверсивные регистры сдвига).

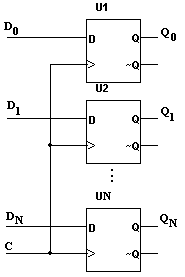

Кроме последовательных

регистров сдвига существуют параллельные

регистры, в

которых информация подается

одновременно на все Nтриггеров и считывается одновременно

с выходов всех триггеров регистра (рис.

6.37). Тактовая частота подается одновременно

на все триггеры.

Рис.

6.38. Моделирование параллельного регистра

в Multisim

Параллельные

регистры используются для хранения

двоичной информации небольшого объема

в течение короткого промежутка времени.

Счетчики.

Счетчики.

Счетчиком называется

устройство, подсчитывающее число входных

импульсов. Число, представляемое

состоянием его выходов по фронту каждого

входного импульса, изменяется на единицу.

Счетчик состоит из nпоследовательно соединенных счетных

триггеров, причем выход одного счетного

триггера соединен с тактовым входом

следующего триггера. Счетчики бывают

суммирующими (прямой счет) и вычитающими

(обратный счет). В суммирующих счетчиках

каждый входной импульс увеличивает

число на его выходах на единицу, в

вычитающих счетчиках уменьшает это

число на единицу. Для того чтобы построить

суммирующий счетчик, необходимо счетный

вход очередного триггера подключить

к инверсному выходу предыдущего (рис.

6.39).

Рис.

6.39. Суммирующий

счетчик и диаграмма его работы

Рис.

6.40. Моделирование суммирующего счетчика

в Multisim

Для того чтобы

изменить направление счета (реализовать

вычитающий счетчик), необходимо счетный

вход очередного триггера подключить к

прямому выходу предыдущего, при этом

изменяется последовательность

переключения триггеров (рис. 6.41).

Счетчик характеризуется

числом состояний в течение одного

периода (цикла). Для двоичных счетчиков

полный цикл счета N=2nот состояния 0..000 до состояния 1…11. Число

состояний называется коэффициентом

пересчетаKсч,

равным отношению числа импульсовNсна входе к числу импульсовNQстна выходе старшего разряда за период:

![]() .

.

Рис.

6.41. Вычитающий

счетчик и диаграмма его работы

Рис.

6.42. Моделирование вычитающего счетчика

в Multisim

Счетчик характеризуется

числом состояний в течение одного

периода (цикла). Для двоичных счетчиков

полный цикл счета N=2nот состояния 0..000 до состояния 1…11. Число

состояний называется коэффициентом

пересчетаKсч,

равным отношению числа импульсовNсна входе к числу импульсовNQстна выходе старшего разряда за период:

![]() .

.

Если на вход

счетчика подавать периодическую

последовательность импульсов с частотой

fс, то частотаfQна выходе старшего разряда счетчика

будет меньше вKсч

раз:Kсч=fс/fQ.

Поэтому счетчики также называют

делителями частоты, аKсч– коэффициентом деления. Для увеличения

величиныKсчнужно увеличить число триггеров в

цепочке. Каждый дополнительный триггер

удваивает число состояний счетчика и

числоKсч.

Д ешифраторы.

ешифраторы.

Комбинационной

называется логическая схема, реализующая

однозначное соответствие между значениями

входных и выходных сигналов. Дешифратор

– логическая комбинационная схема,

имеющая nинформационных

входов и 2nвыходов. Каждой комбинации логических

уровней на входах будет соответствовать

активный уровень на одном из 2nвыходов. Как любая логическая схема,

дешифратор может быть задан таблицей

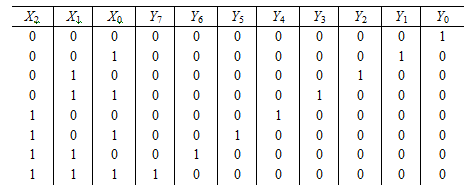

истинности. Таблица истинности дешифратора

3х8 (табл. 6.3) состоит из трех столбцов,

соответствующих входным сигналамХ0,Х1,Х2, и восьми

столбцов, соответствующих выходным

сигналамY0,Y1,Y2,Y3,Y4,Y5,Y6,Y7.

В первых слева трех столбцах расположены

возможные комбинации входных сигналов,

а в последних восьми – соответствующие

им комбинации выходных сигналов.

Т

а б л и ц а 6.3

Схема имеет восемь

выходов, на одном из которых потенциал

высокий, на остальных низкий. Номер

единственного выхода, имеющего высокий

потенциал, соответствует двоичному

числу, формируемому состояниями входных

сигналов. Этот принцип формирования

выходного сигнала можно описать следующим

образом: Yi= 0, еслиi=k;Yi= 1, еслиi≠k,

здесьi– номер разряда;k= 22 X2+ 21X1 +

20X0.

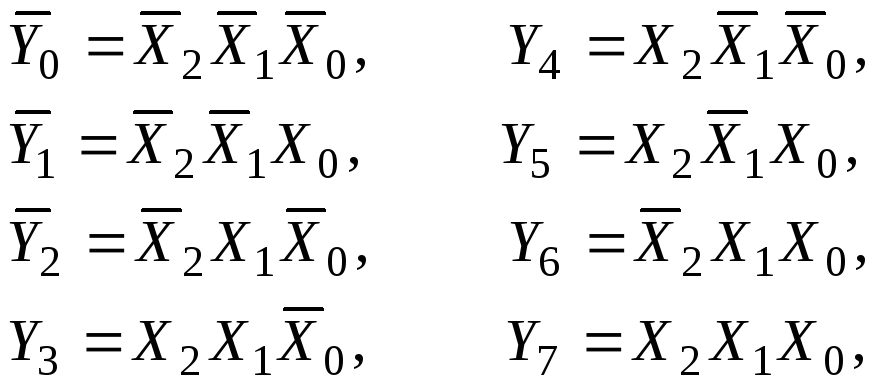

Выражения для

каждого выхода дешифратора:

где «¯» –

инвертирование.

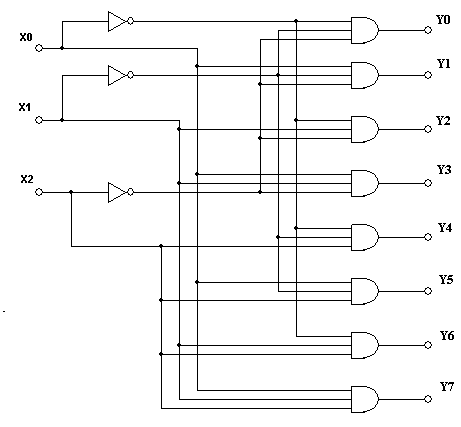

Таким образом,

схема дешифратора должна содержать три

схемы «НЕ» и восемь схем «3И» (рис. 6.43).

Рис.

6.43. Схема

дешифратора 3х8

Рис.

6.44. Моделирование дешифратора 3х8 в

Multisim

Профи

(672),

на голосовании

12 лет назад

Дополнен 12 лет назад

блок в виде т-триггера

Дополнен 12 лет назад

где в программе пункт создания таких блоков

Голосование за лучший ответ

Серж Бури

Просветленный

(39345)

12 лет назад

Не знаю как в всё устроено в Multisim 8, а в Multisim 10 (русифицированной) на панели меню есть пункт ЦИФРОВЫЕ МИКРОСХЕМЫ. Так вот там среди кучи буржуйских стандартных элементов TIL есть компонент T_FF(T-flip-flop).Это и есть Т триггер в его буржуйском обозначении. Как изобразить его по госту не в курсе, ведь главная задача Multisim это отработка принципиальных схем и выдача данных для изготовления печатных плат промоделированного электронного устройства.

Лабораторная

работа

Тема: «Исследование

принципа работы Т-триггера, D-триггера, JK-триггера»

Цель

работы:

изучение функционирования триггеров различных типов, принципов их синтеза и

взаимопреобразования.

Оборудование: персональный

компьютер (монитор, системный блок, клавиатура, мышь), ОС Windows 10,

программа для моделирования электрических схем Multisim .

Теоретические

сведения:

Триггеры

относятся к цифровым схемам последовательностного типа, выходное состояние

которых в любой момент времени определяется как сигнала-

ми на входах триггера, так и его предыдущим состоянием. Триггер является

элементарной ячейкой памяти, а также служит основой для построения делите-

лей частоты, счетчиков и регистров.

В

каждый конкретный момент времени триггер может находиться только в

одном из возможных устойчивых состояний, поддерживаемых за счет действия

обратных связей. Переход устройства из одного состояния в другое осуществляется

под действием внешних управляющих сигналов.

Триггер

имеет два выхода: прямой Q и инверсный Q .

Число

входов зависит от структуры и функций, выполняемых триггером.

В зависимости от алгоритма работы триггер может иметь установочные, ин-

формационные и управляющие входы. Установочные входы устанавливают со-

стояние триггера независимо от состояния других входов. Входы управления

разрешают запись данных, подающихся на информационные входы.

Приняты

следующие обозначения входов триггеров:

–

S (Set – установка) – вход установки триггера в единичное состояние по

прямому выходу Q;

–

R (Reset – сброс)и – вход сброса триггера в нулевое состояние по прямому выходу

Q;

–

J (Jerk) – является входом установки триггера в единичное состояние;

-K

(Kill) – является входом установки триггера в нулевое состояние;

-D

(Data, Delay) – информационный вход. На него подается информация,

предназначенная для записи в триггер;

-Т

(Тoggle) – счетный вход;

-C

(Clock) – вход синхронизации.

В

зависимости от логической структуры различают триггеры с прямыми и

инверсными входами. Триггеры с прямыми входами строятся на логических

элементах 2 ИЛИ-НЕ (активным сигналом является сигнал логической едини-

цы). Триггеры с инверсными входами строятся на логических элементах 2 И-

НЕ (активный сигнал – логический ноль).

Тип

триггера определяется алгоритмом его работы и способом записи ин-

формации. Примерная классификация представлена на рисунке 1.

Рисунок 1.

– Классификация триггеров

У асинхронных

триггеров переключение (запись информации) происходит

под действием информационных сигналов. Такие триггеры имеют только ин-

формационные входы.

У синхронных

триггеров запись информации происходит под действием

разрешающих сигналов синхронизации.

Синхронные триггеры со статическим управлением (управление по уровню

синхросигнала, level-sensitive) принимают информационные сигналы все

время, пока действует импульс синхронизации. Следовательно, за время действия

импульса синхронизации переключение триггера может быть многократным.

Синхронные

триггеры с динамическим управлением (управление по фронту

синхросигнала, edge-sensitive) принимают только те информационные сигналы,

которые были на информационных входах к моменту прихода синхронизирующего

импульса. Динамический вход изображают на схемах треугольником.

Если вершина треугольника обращена в сторону микросхемы (прямой динами-

ческий вход), то триггер срабатывает по фронту входного импульса, если от нее

(инверсный динамический вход) – по срезу импульса (рисунок 2).

Фронтом сигнала

называется переход цифрового сигнала из состояния

«ноль» (нижний уровень) в состояние «единица» (верхний уровень) или

наоборот.

рисунок

2. Временная диаграмма сигнала синхронизации

Отрезок времени t1

– t2 соответствует времени длительности положительного фронта сигнала (фронту),

отрезок времени t3–t4 соответствует времени длительности отрицательного фронта

синхросигнала (спаду). В эти моменты времени происходит переключение триггеров

с динамическим управлением. Отрезок времени t2 – t3 соответствует времени

длительности синхросигнала. В этом

промежутке времени происходит переключение триггеров со статическим

управлением.

RS-триггер

– триггер с раздельной установкой состояний логического ну-

ля и единицы, имеющий два информационных входа S и R.

Работа асинхронного RS-триггера описывается таблицей переключений

(таблица 1).

Таблица 1 –

Таблица истинности асинхронного RS-триггера

|

Значения исходных параметров |

Состояние выхода |

|||||

|

Логика ИЛИ-НЕ |

Логика И-НЕ |

|||||

|

R |

S |

Qn |

Qn |

Qn+1 |

||

|

0 |

0 |

0 |

0 |

Qn |

Запрет |

|

|

0 |

0 |

1 |

1 |

|||

|

0 |

1 |

0 |

1 |

Установка |

0 |

Установка |

|

0 |

1 |

1 |

1 |

0 |

||

|

1 |

0 |

0 |

0 |

Установка |

1 |

Установка |

|

1 |

0 |

1 |

0 |

1 |

||

|

1 |

1 |

0 |

Запрет |

0 |

Qn |

|

|

1 |

1 |

1 |

1 |

При одновременной подаче переключающих сигналов на оба входа триггер

распадается на два автономных инвертора. При этом на его обоих выходах

устанавливается сигнал одинакового уровня, следовательно, схема теряет

триггерные свойства, и указанные комбинации входных сигналов являются

запрещенными.

При одновременном снятии переключающих сигналов с обоих входов состояние

триггера не изменится. Такое состояние триггера называют режимом

хранения информации, т. к. информация на выходе остается неизменной.

При подаче сигнала

на вход S на прямом выходе триггера устанавливается

значение логической единицы (режим записи). При подаче сигнала на вход R на

прямом выходе триггера устанавливается значение логического нуля (режим

сброса).

В зависимости от логической структуры различают RS-триггеры с прямыми и

инверсными входами. Их схемы и условные обозначения приведены на

рисунке 3. Триггеры такого типа построены на двух логических элементах 2

ИЛИ-НЕ (триггер с прямыми входами на рисунке 3, а) или 2 И-НЕ (триггер с

инверсными входами на рисунке 3, б). Выход каждого из логических элементов

подключен к одному из входов другого элемента, что обеспечивает триггеру два

устойчивых состояния.

а) на

элементах 2 ИЛИ-НЕ; б) на элементах 2 И-НЕ

Рисунок 3

– Схема и условное обозначение асинхронного RS-триггера

Часто сигналы

проходят о через тракты, не обладающие одинаковой задержкой. Поэтому сигналы

попадают на входы схемы неодновременно, что вызывает ложное срабатывание

триггера – эффект «гонок». Чтобы этого не происходило, используют синхронный

RS-триггер.

В синхронном (тактируемом) RS-триггере процесс переработки информации

упорядочивается во времени с помощью специальных тактовых сигналов,

вырабатываемых общим для всего устройства генератором. Синхронный RS-

триггер имеет дополнительный синхронизирующий вход C (статический или

динамический). Условное графическое изображение синхронного RS-триггера

показано на рисунке 4.

Рисунок 4

– Схема и условное обозначение синхронного RS-триггера

на элементах 2 И-НЕ

JK-триггер

отличается от RS-триггера тем, что в нем устранена неопределенность, которая

возникает в RS-триггере при некоторой комбинации входных

сигналов (нет запрещенных комбинаций).

JK-триггеры называют

универсальными, т. к. они могут выполнять функции RS-, T- и D-триггеров.

Универсальный

JK-триггер

имеет два информационных входа J и K. По входу J триггер устанавливается в

состояние Q = 1, Q = 0 , а по входу K – в состояние Q = 0, Q = 1.

Комбинированный

JK-триггер имеет дополнительные асинхронные входы S и R для предварительной

установки триггера в определенное состояние (логической 1 или 0).

Простейший

JK-триггер можно получить из синхронного RS-триггера, если ввести

дополнительные обратные связи с выходов триггера на входы, которые позволяют

устранить неопределенность в таблице состояний (рисунок 5).

Рисунок 5

– Преобразование синхронного RS-триггера в JK-триггер Таблица состояний

JK-триггера с прямыми входами приведена в таблице

Таблица состояний

JK-триггера с прямыми входами приведена в таблице 2.

При входных сигналах J = K = 0 состояние триггера не изменяется, т. к.

напряжение низкого уровня на одном входе элемента И-НЕ отменяет прохождение

сигналов от других его входов и удерживает выходной сигнал на высоком

уровне. При подаче на входы J и K одновременно напряжений высокого уровня

триггер переключается в состояние, противоположное предыдущему.

Таблица 2 –

Состояния асинхронного JK-триггера

|

Исходные параметры |

Состояния выхода |

|||

|

Состояние в момент времени n |

J |

K |

Qn+1 |

|

|

Qn |

0 |

0 |

Qn |

Хранение |

|

Qn |

0 |

1 |

1 |

Запись |

|

Qn |

1 |

0 |

0 |

Запись |

|

Qn |

1 |

1 |

Qn |

Инверсия |

D-триггер

(триггер-защелка) – триггер с одним информационным входом,

работающий так, что сигнал на выходе после переключения равен сигналу на

входе D до переключения (рисунок 6).

Основное

назначение D-триггеров – задержка сигнала, поданного на вход D.

Он имеет информационный вход D (вход данных) и вход синхронизации C

(статический или динамический). В таком триггере информация на выходе может

быть задержана на один такт по отношению к входной информации.

Рисунок 6

– D-триггер на элементах И-НЕ

D-триггер возможно

получить из синхронного RS-триггера, если ввести

дополнительный инвертор между входами R и S. В таком триггере состояние

неопределенности для входов R и S исключается, т. к. инвертор формирует на

входе R сигнал S . Из JK-триггера также можно получить D-триггер, если вход

соединить с входом J через дополнительный инвертор (рисунок 7).

Комбинированные

D-триггеры имеют дополнительные входы асинхронной установки логических нуля и

единицы – входы S и R.

Рисунок 7

– Преобразование JK- в D-триггер

D-триггер в

основном используется для реализации защелки. Например,

для снятия 32 бит информации с параллельной шины берут 32 D-триггера и

объединяют их входы синхронизации для управления записью информации в

защелку, а 32 D-входа подсоединяют к шине.

T-триггер (счетный

триггер) по каждому такту изменяет свое логическое

состояние на противоположное при единице на входе Т и не изменяет выходное

состояние при нуле на входе. Такой триггер имеет один управляющий вход T.

Он может быть построен на JK-триггере путем объединения входов J, K и

C (т. е. J = K = C = T). Также он может быть построен на D-триггере путем со-

единения инверсного выхода с входом D и подачей на вход С счетных импульсов, в

результате чего триггер при каждом счетном импульсе будет переключаться в

противоположное состояние (рисунок 8).

Рисунок 8

– Преобразование JK- и D-триггеров в T-триггер

Характерной

особенностью Т – триггеров является то, что частота изменения выходных сигналов

в два раза меньше частоты входных. Это свойство Т-

триггеров используется при построении на их основе делителей частоты (на Т-

вход подают единицу, а на С – сигнал с частотой, которая будет поделена) и

двоичных счетчиков.

Задание: Исследовать

работу Т – триггера в счетном режиме, D – триггера, JK –

триггера. Получить временные диаграммы работы исследуемых триггеров.

Порядок

выполнения работы:

1.Ознакомиться с

теоретической частью.

2.Собрать схему в

соответствии с рисунком 9 и исследовать работу

T-триггера, D-триггера и JK-триггера. Работа RS-триггера из-за наличия

запрещенных комбинаций не исследуется.

Тактовые импульсы

(прямоугольной формы) с выхода генератора сигналов

XFG1 с амплитудой 5 В и частотой F Гц подаются на синхровходы триггеров и

на вход анализатора XLA1. Частота работы внутреннего тактирующего источника

генератора бинарного слова – 1кГц, логического анализатора – 10 кГц (установки

по умолчанию).

Сигналы J, K, а

также значения F берутся из таблицы 3 в соответствии с

номером варианта.

3.Исследовать

работу Т-триггера в счетном режиме, для чего на Т-вход

необходимо подать сигнал логической единицы, на синхровход – сигнал с

генератора импульсов.

4.Получить

временные диаграммы работы исследуемых триггеров.

Рисунок 9

– Схема исследования T-, D- и JK-триггера

Таблица 3.

Кодовые комбинации для исследования триггеров

|

Вариант 1 |

Вариант 2 |

Вариант 3 |

Вариант 4 |

Вариант 5 |

Вариант 6 |

||||||

|

Сигналы |

Сигналы |

Сигналы |

Сигналы |

Сигналы |

Сигналы |

||||||

|

J |

K |

J |

K |

J |

K |

J |

K |

J |

K |

J |

K |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

|

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

|

F=1кГц |

F=2кГц |

F=1кГц |

F=1,5кГц |

F=1кГц |

F=2кГц |

||||||

|

Примечание-значения |

Контрольные

вопросы и задания.

1.Приведите

определение триггера, перечислите его отличительные особенности.

2.Какие признаки используют при классификации триггеров? 3.Какие

триггеры называются асинхронными, а какие синхронными?

4.Какой тип триггеров называется «универсальным» и почему? 5.

Приведите определение, схему, условное обозначение и принцип работы

RS-триггера. 6. Приведите определение, схему, условное обозначение и принцип

работы D-триггера.

7. Приведите определение, схему, условное обозначение и принцип работы

JK-триггера.

8. Приведите определение, схему, условное обозначение и принцип работы

T-триггера.

Содержание

отчета по лабораторной работе

1. № и наименование (тема) работы;

2. цель работы;

3. оборудование;

4. теоретические сведения;

5. задание;

6. порядок

выполнения /ход работы/: подробные записи по выполнению заданий (Схема

исследования триггеров различных типов, Структурные схемы и временные диаграммы

для каждого исследованного триггера) полученные результаты;

7. ответы на вопросы;

8. выводы по выполненной работе;

Слайд 1

Описание слайда:

Триггер. D-триггер. Программирование в Lab View и в Multisim.

Подготовили отчет

Студентки 231 группы

Факультета КНиИт

Латышева Анастасия

Юдина Татьяна

Слайд 2![Триггер

Триггер (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознаётся по значению выходного напряжения. По характеру действия триггеры относятся к импульсным устройствам — их активные элементы (транзисторы, лампы) работают в ключевом режиме, а смена состояний длится очень короткое время[1].](https://myslide.ru/documents_3/e9796eb5a7156474aa31fbf2ac68d6fa/img1.jpg)

Описание слайда:

Триггер

Триггер (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознаётся по значению выходного напряжения. По характеру действия триггеры относятся к импульсным устройствам — их активные элементы (транзисторы, лампы) работают в ключевом режиме, а смена состояний длится очень короткое время[1].

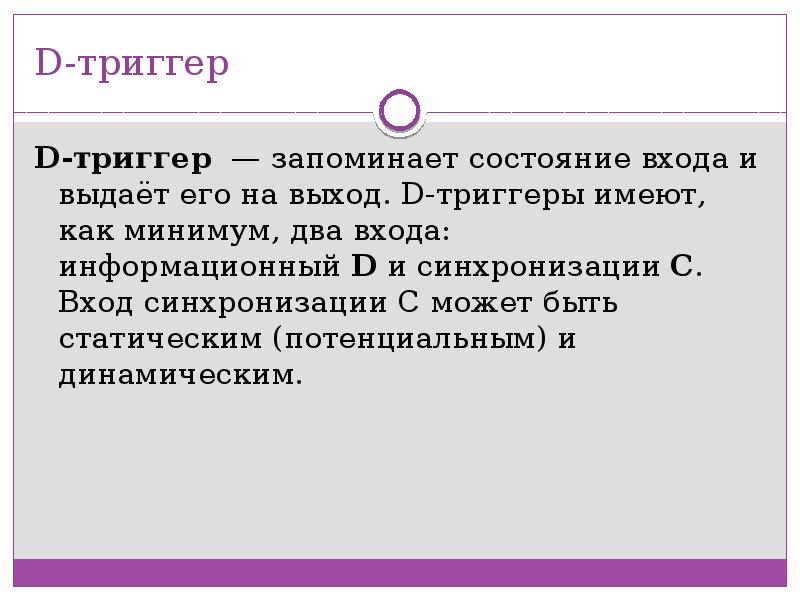

Слайд 3

Описание слайда:

D-триггер

D-триггер — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. Вход синхронизации С может быть статическим (потенциальным) и динамическим.

Слайд 4![D-триггер

D-триггер на 6 логических элементах И-НЕ, переключающийся по положительному фронту: а) функциональная схема; б) таблица функционирования; в)условное графическое обозначение[3].](https://myslide.ru/documents_3/e9796eb5a7156474aa31fbf2ac68d6fa/img3.jpg)

Описание слайда:

D-триггер

D-триггер на 6 логических элементах И-НЕ, переключающийся по положительному фронту: а) функциональная схема; б) таблица функционирования; в)условное графическое обозначение[3].

Слайд 5![D-триггер

Функционирование D-триггера, переключающегося по положительному фронту[3].](https://myslide.ru/documents_3/e9796eb5a7156474aa31fbf2ac68d6fa/img4.jpg)

Описание слайда:

D-триггер

Функционирование D-триггера, переключающегося по положительному фронту[3].

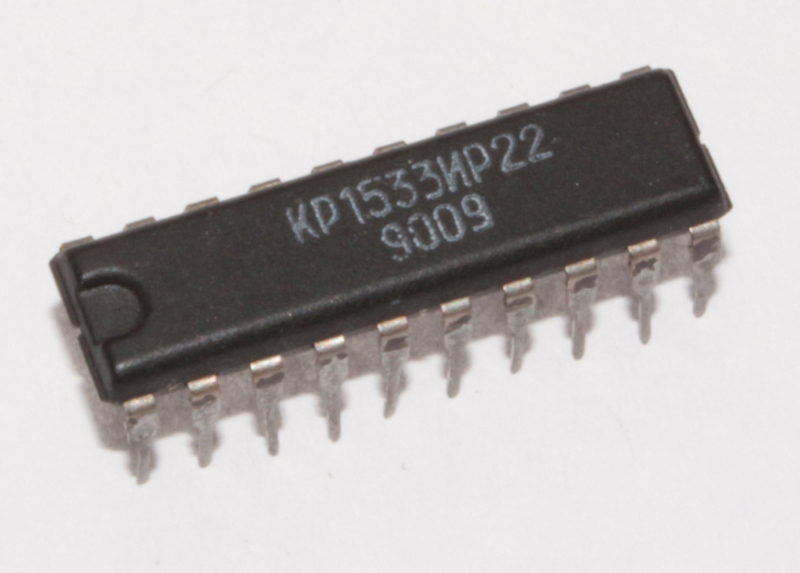

Слайд 6![К155ТМ2

Нам была выдана микросхема К155ТМ2, которая представляет собой два независимых D-триггера, срабатывающих по положительному фронту тактового сигнала[2].](https://myslide.ru/documents_3/e9796eb5a7156474aa31fbf2ac68d6fa/img5.jpg)

Описание слайда:

К155ТМ2

Нам была выдана микросхема К155ТМ2, которая представляет собой два независимых D-триггера, срабатывающих по положительному фронту тактового сигнала[2].

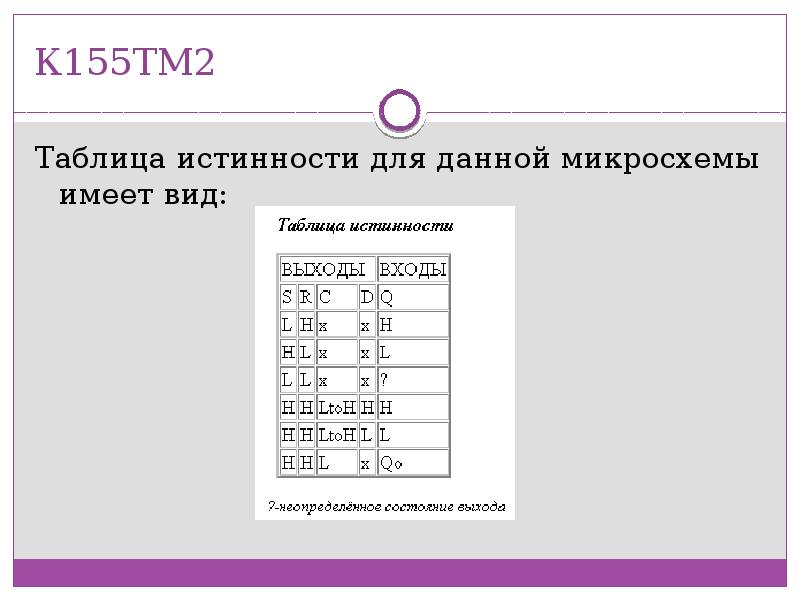

Слайд 7

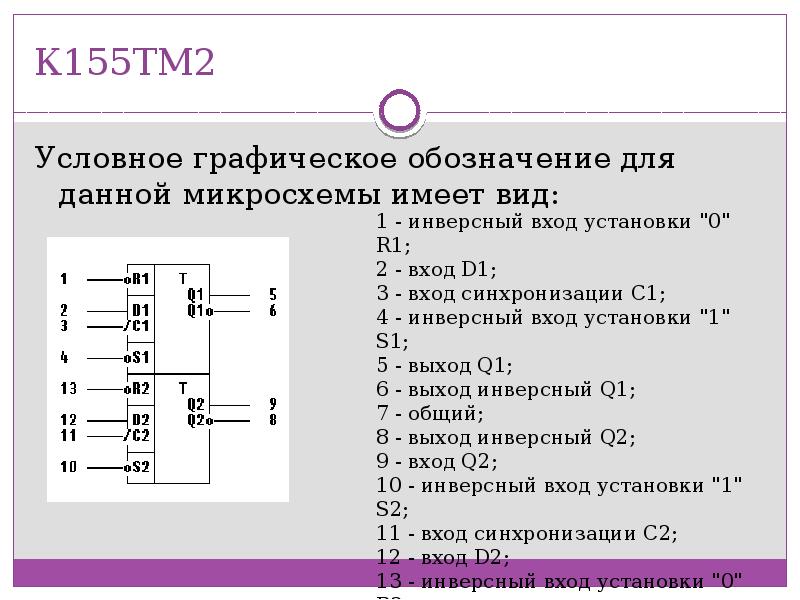

Описание слайда:

К155ТМ2

Таблица истинности для данной микросхемы имеет вид:

Слайд 8

Описание слайда:

К155ТМ2

Условное графическое обозначение для данной микросхемы имеет вид:

Слайд 9

Описание слайда:

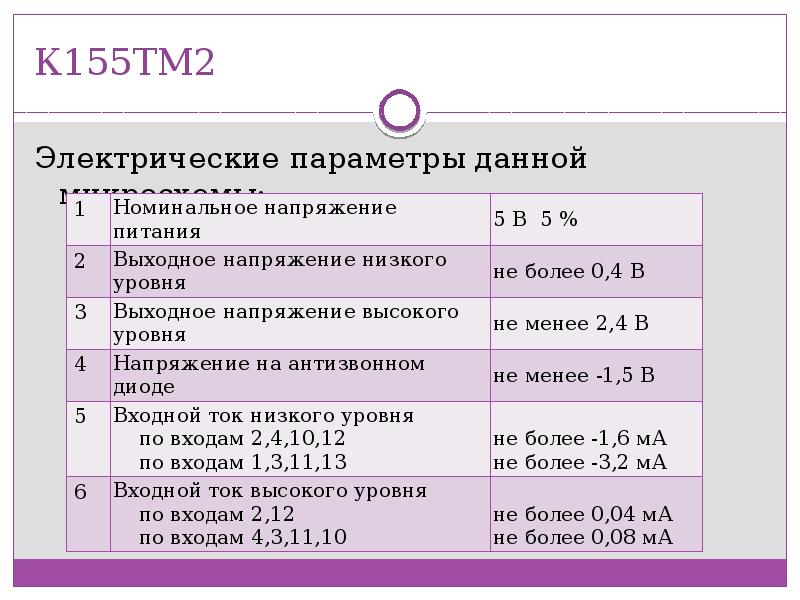

К155ТМ2

Электрические параметры данной микросхемы:

Слайд 10

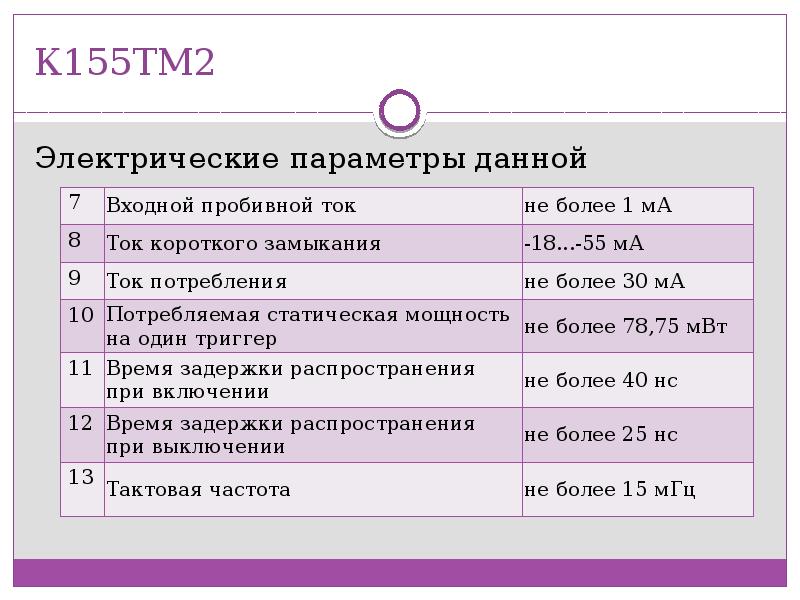

Описание слайда:

К155ТМ2

Электрические параметры данной микросхемы:

Слайд 11

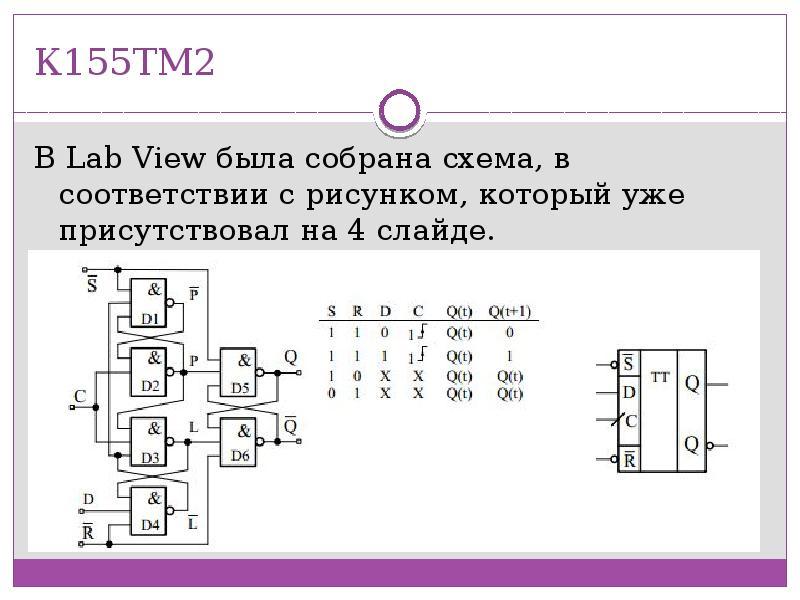

Описание слайда:

К155ТМ2

В Lab View была собрана схема, в соответствии с рисунком, который уже присутствовал на 4 слайде.

Слайд 12

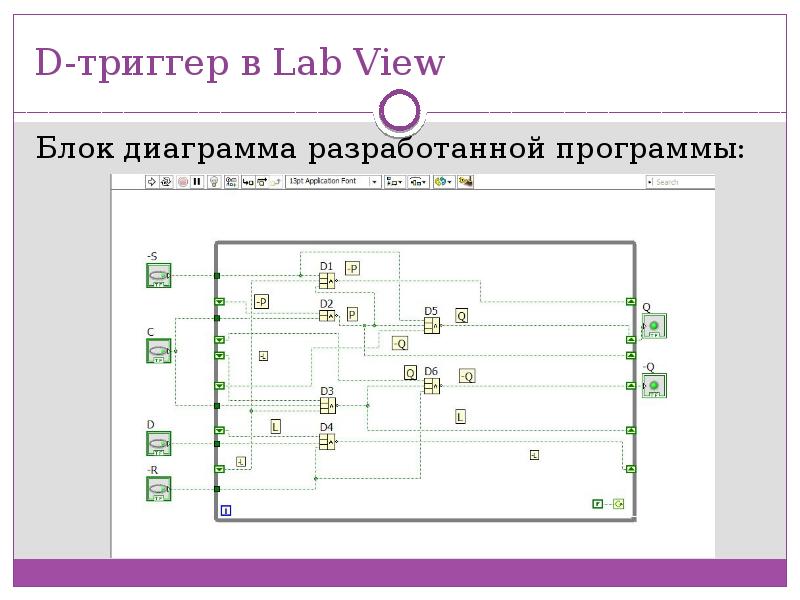

Описание слайда:

D-триггер в Lab View

Блок диаграмма разработанной программы:

Слайд 13

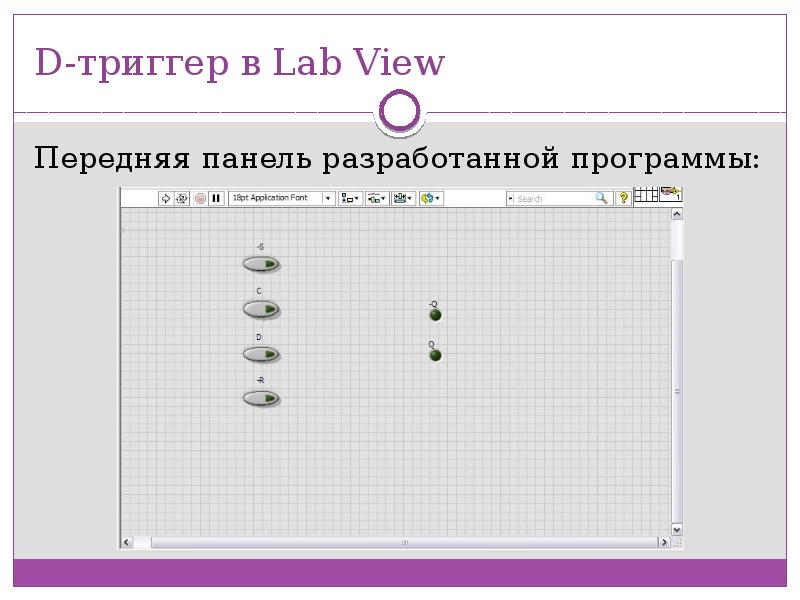

Описание слайда:

D-триггер в Lab View

Передняя панель разработанной программы:

Слайд 14

Описание слайда:

D-триггер в Lab View

Проверка корректности работы разработанной программы:

Слайд 15

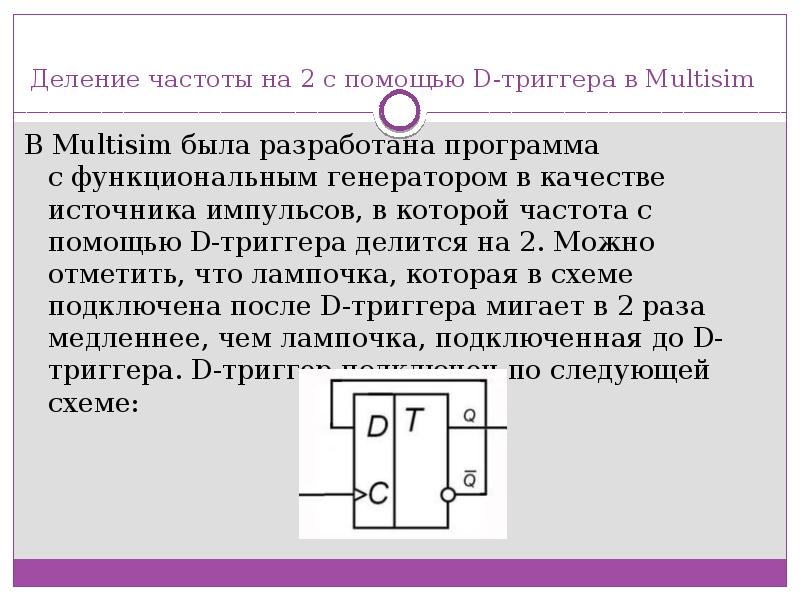

Описание слайда:

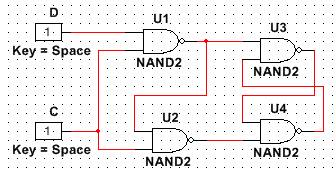

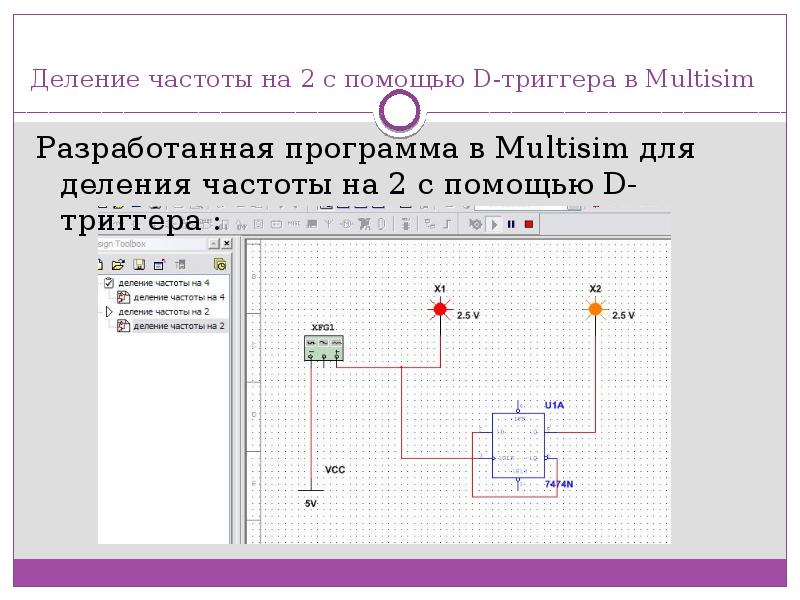

Деление частоты на 2 с помощью D-триггера в Multisim

В Multisim была разработана программа с функциональным генератором в качестве источника импульсов, в которой частота с помощью D-триггера делится на 2. Можно отметить, что лампочка, которая в схеме подключена после D-триггера мигает в 2 раза медленнее, чем лампочка, подключенная до D-триггера. D-триггер подключен по следующей схеме:

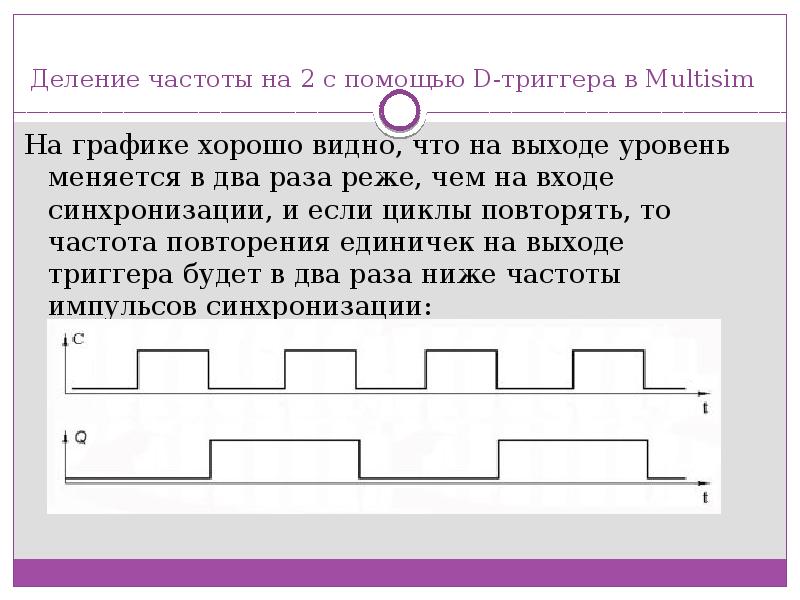

Слайд 16

Описание слайда:

Деление частоты на 2 с помощью D-триггера в Multisim

На графике хорошо видно, что на выходе уровень меняется в два раза реже, чем на входе синхронизации, и если циклы повторять, то частота повторения единичек на выходе триггера будет в два раза ниже частоты импульсов синхронизации:

Слайд 17

Описание слайда:

Деление частоты на 2 с помощью D-триггера в Multisim

Разработанная программа в Multisim для деления частоты на 2 с помощью D-триггера :

Слайд 18

Описание слайда:

Деление частоты на 4 с помощью двух

D-триггеров в Multisim

В Multisim была разработана программа с функциональным генератором в качестве источника импульсов, в которой частота с помощью двух D-триггеров делится на 4. Можно отметить, что лампочка, которая в схеме подключена после первого D-триггера мигает в 2 раза медленнее, чем лампочка, подключенная до первого D-триггера. А лампочка, подключенная после второго D-триггера, мигает в 4 раза медленнее, , чем лампочка, подключенная до первого D-триггера, и, следовательно, в 2 раза медленнее, чем лампочка, подключенная между первым и вторым , чем лампочка, подключенная до первого D-триггером.

Слайд 19

Описание слайда:

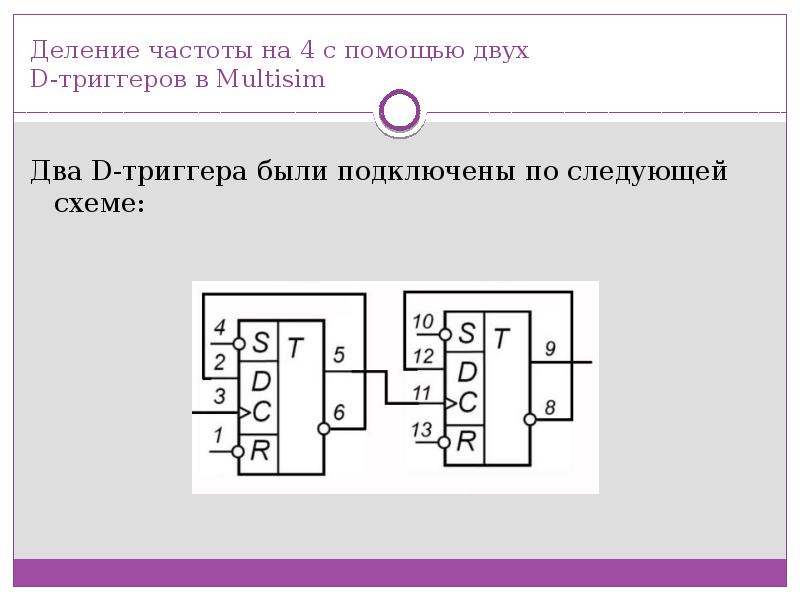

Деление частоты на 4 с помощью двух

D-триггеров в Multisim

Два D-триггера были подключены по следующей схеме:

Слайд 20

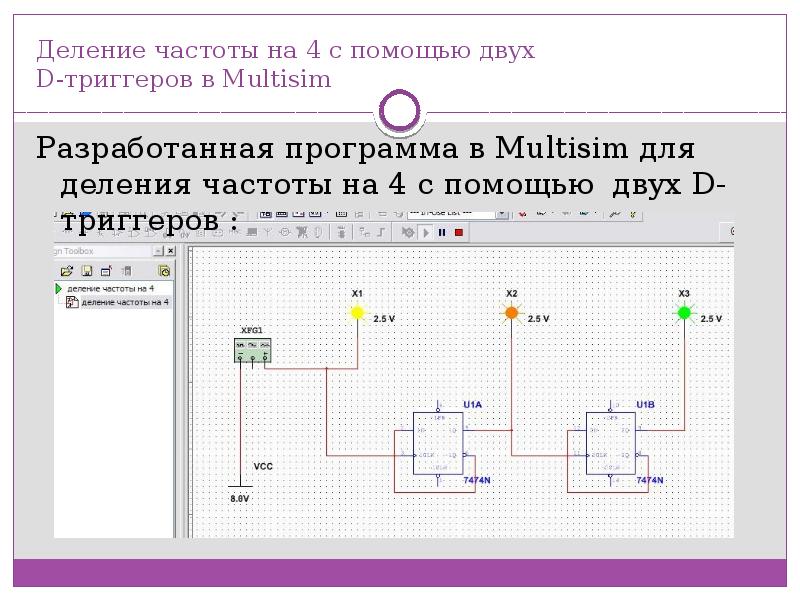

Описание слайда:

Деление частоты на 4 с помощью двух

D-триггеров в Multisim

Разработанная программа в Multisim для деления частоты на 4 с помощью двух D-триггеров :

Слайд 21![Список использованных источников

1. Статья «Триггер»

[Электронный ресурс]/URL:

https:// ru.wikipedia.org/wiki/Триггер

2. Статья «К155ТМ2»

[Электронный ресурс]/URL: http://www.chipinfo.ru/dsheets/ic/155/tm2.html

3. В. А. Потехин, Схемотехника цифровых устройств, В-Спектр, Томск-2012](https://myslide.ru/documents_3/e9796eb5a7156474aa31fbf2ac68d6fa/img20.jpg)

Описание слайда:

Список использованных источников

1. Статья «Триггер»

[Электронный ресурс]/URL:

https:// ru.wikipedia.org/wiki/Триггер

2. Статья «К155ТМ2»

[Электронный ресурс]/URL: http://www.chipinfo.ru/dsheets/ic/155/tm2.html

3. В. А. Потехин, Схемотехника цифровых устройств, В-Спектр, Томск-2012